# FOR REFERENCE ONLY

# The Nottingham Trent University Libraries & Learning Resources SHORT LOAN COLLECTION

THIS ITEM MAY NOT BE RENEWED

ProQuest Number: 10290325

All rights reserved

INFORMATION TO ALL USERS The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

ProQuest 10290325

Published by ProQuest LLC (2017). Copyright of the Dissertation is held by the Author.

All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code Microform Edition © ProQuest LLC.

> ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 – 1346

# Feasibility of micro-mirror Laterally-Emitting Thin-Film Electroluminescent Devices for an Opto-Electronic Integrated Circuit

# Sharon Phooi San THENG B.Eng (Hons)

A thesis submitted in partial fulfilment of the requirements of The Nottingham Trent University for the degree of Doctor of Philosophy

Department of Electrical and Electronic Engineering The Nottingham Trent University Nottingham, U.K.

### **June 2001**

This copy of thesis has been supplied on condition that anyone who consults it is understood to recognise that its copyright rests with the author and that no information derived from it may be published without the author's prior written consent.

「ないたい」のないであるというというないない

### Abstract

The design and development of micro-mirror Laterally-Emitting Thin-Film Electroluminescent (mmLETFEL) devices aiming at image bar array applications such as electrophotographic printing has been one of the main objectives for the Optical Device Engineering Group at The Nottingham Trent University. This thesis describes the work carried out in determining the potential and possibility of developing the current mmLETFEL technology as an integrated optical device. In particular, assessing the feasibility and commercial viability for a novel Opto-Electronic Integrated Circuit (OEIC) – the mmLETFEL device integrated with the corresponding drive circuitry.

The initial investigation explores the feasibility of the current LETFEL technology in producing sufficient emission for exposing a photoconductively charged photoreceptor. The luminance observed from the edge emission of a LETFEL test device, has been found to discharge a commercial photoconductive drum, at 50% gain, and at a print speed of 13 p.p.m.

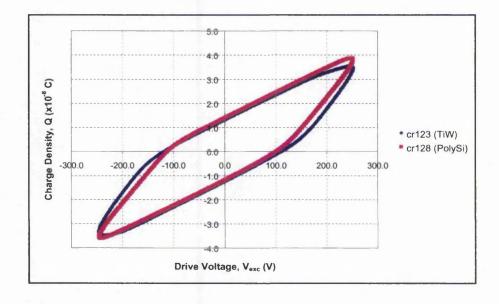

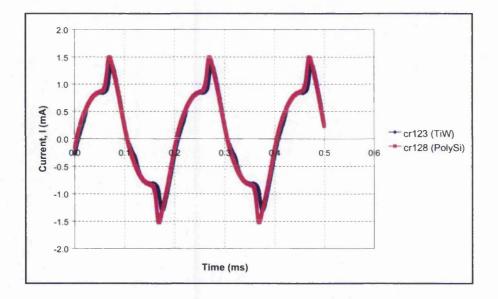

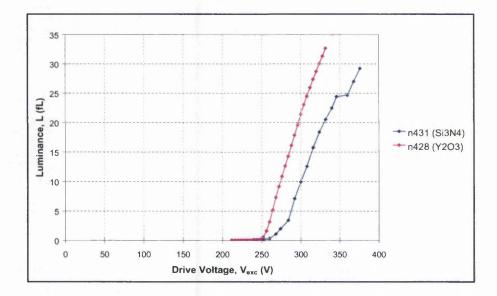

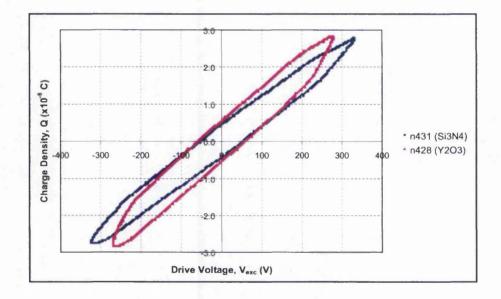

The fabrication of mmLETFEL test devices that are suitable for integration has been successful. This includes pre-fabricating base electrodes of PolySi and TiW materials, defined prior to the deposition of the mmLETFEL structure, and with insulators of  $Y_2O_3$  and  $Si_3N_4$ . Results from the electro-optical characterisation of these four configurations of mmLETFEL device structures have demonstrated that  $Y_2O_3$  supersedes  $Si_3N_4$  material as an appropriate dielectric, in that the luminance versus drive voltage (L-V) curve exhibits a comparatively steeper slope and lower device threshold, which are both desirable for mmLETFEL device activation. Characteristics of mmLETFEL test devices grown with base electrodes PolySi and TiW have been comparable, and this indicates that the deposition of these two materials have no significant effect on the mmLETFEL device performance.

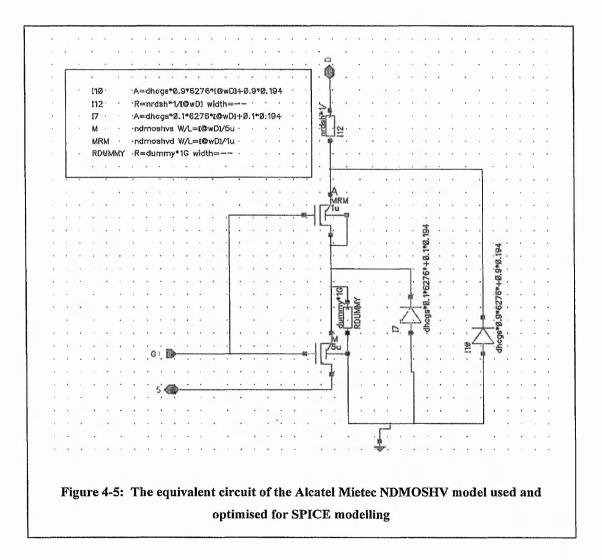

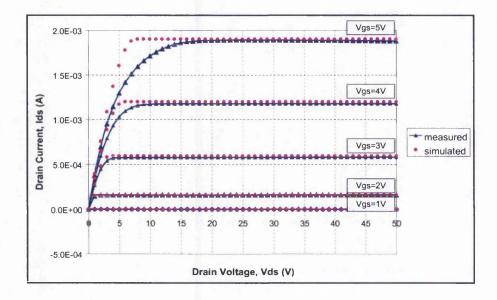

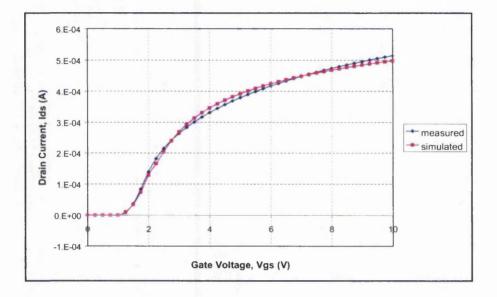

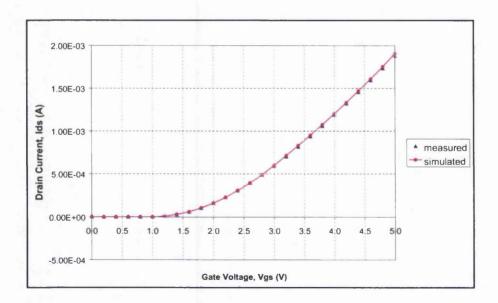

SPICE modelling has been conducted on commercially available drivers from various fabrication houses based on the SPICE model parameters obtained from these manufacturers. Due to cost and technology accessibility, the 100V process DMOS device from Alcatel Mietec in Belgium has been selected for further investigation. Electrical characterisation and SPICE modelling have been performed on test dies (of the NDMOSHV model) obtained via EuroPractice. Comparison between the measured and simulated results shows a <10% error margin in the saturation region for the transistor output characteristics, and a <5% error margin for the transistor transfer characteristics.

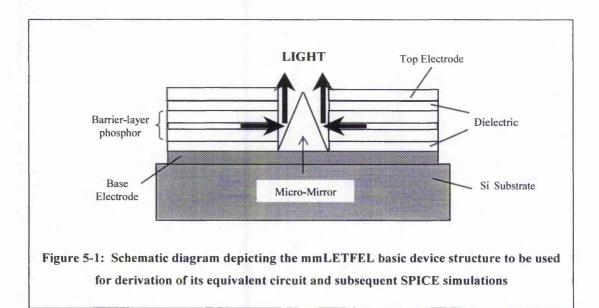

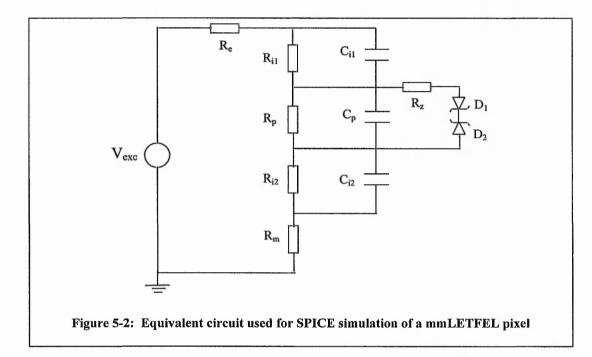

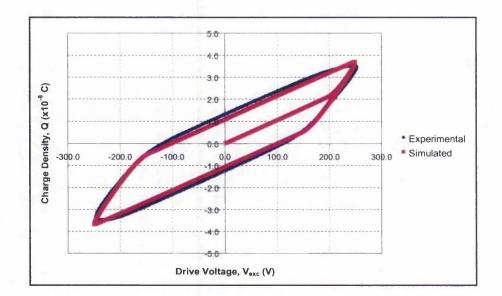

This leads to circuit simulation using SPICE of the novel integrated mmLETFEL pixel – combining the developed mmLETFEL model and the optimised NDMOSHV model. By using previously characterised results of the mmLETFEL test devices to form a simple equivalent circuit, and the optimised SPICE parameters of the NDMOSHV model from Alcatel Mietec, the OEIC equivalent circuit has been developed and theoretically simulated for its performance.

Consequently, the processing route for an integrated mmLETFEL pixel is proposed, utilising the materials previously determined for the insulators and base electrodes. In addition, the results of the latest developments to the mmLETFEL technology from the aspects of fabrication, outcoupling efficiency, and overall performance, that are being investigated concurrently, have influenced the outcome of this research.

ii

# Acknowledgements

The following people and organisations have been my support, my inspiration, my strength, and my encouragement; to whom my sincerest thanks and utmost appreciation are extended:

My supervisors and mentors, Professor Clive Thomas, Dr Wayne Cranton, and Dr Robert Stevens, for their advice and guidance throughout this research programme.

Dr Costas Tsakonas, and Dr Robert Ranson, for their contributions to the fabrication of the mmLETFEL test wafers.

Dr Sara Barros for her time and support, both professionally and personally, during the course of this programme.

Murugesan Sethu, for his assistance in the characterisation of the mmLETFEL test devices.

The other members of the Displays Research Group, Alan Liew, and Demos Koutsogeourgis, for providing a fun working environment.

NMRC in Cork, Ireland, for their contributions to the fabrication of the silicon base wafers, with micro-mirrors and underlying base electrodes; especially Brendan O'Neill, for the provision of the process details.

Qudos in RAL, Oxford, for their contributions to the post-processing of the mmLETFEL test wafers; especially Dr Marc Craven, for the provision of the process details.

Alcatel Mietec in Belgium, and EuroPractice, for the provision of the Alcatel Mietec driver test die, design rules, and model parameters; especially Dr Zhen Qiu Ning, for his assistance in the SPICE modelling of the corresponding Alcatel Mietec driver technology.

Holtek, and UMC, in Taiwan, and Supertex in the U.S., for their contributions in part to the provision of test die and SPICE model parameters of their respective driver technologies.

Hans Sporrel from Silvaco International, Stephen Bell and Hugo Van Hove from EuroPractice Software Support, and Dr Joe Rodriquez from Bradford University, for their valuable advice in the SPICE modelling of high-voltage drivers.

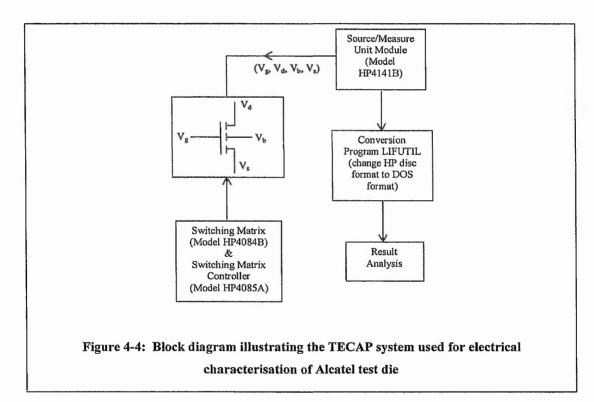

Stephen Thomas, for his assistance in using the TECAP system at RAL, Oxford, for the characterisation of the Alcatel Mietec high-voltage driver test die.

Dr J Verez, and Dr C Juhasz, from Imperial College, London, for their knowledge and discussion of photoconductive materials.

Finally, my wonderful friends here in the U.K., who have helped steer me through many rough spots and stood by me during those periods of difficulties.

Last but not least, my dearest family and friends back home in Malaysia, for their continued love and affection, their unending support and encouragement throughout this journey, and their unwavering faith in my eventual success.

# **Publications**

"Laterally Emitting Thin Film Electroluminescence for Head Mounted Displays"; W M Cranton, C B Thomas, R Stevens, M R Craven, S O Barros, E A Mastio and P S Theng; *Proceedings of the Electronic Information Displays Symposium (EID 1997), London, U.K.*

"Feasibility of Laterally-Emitting Thin-Film ElectroLuminescent (LETFEL) Devices for an Opto-Electronic Integrated Circuit (OEIC)"; P S Theng, W M Cranton, C B Thomas, C Tsakonas and R Stevens; *Proceedings of the Society of Information Displays Symposium (SID 2000), Long Beach, California, U.S.A.*

"An Integrated High-Resolution High-Intensity Micro-Mirror Laterally-Emitting Thin-Film Electroluminescent (mmLETFEL) Device for Electrophotographic Printing"; P S Theng, W M Cranton and C B Thomas; *under review at the time of writing*.

v

# and a start of the start of the

# **Statement of Work**

Fabrication of the mmLETFEL test devices on silicon base wafers pre-fabricated with reflecting micro-structures and different base electrode materials, i.e. titanium/tungsten (TiW) and polysilicon (PolySi).

Optical (Luminance versus Drive Voltage) and Electrical (Charge versus Drive Voltage) Characterisation of the mmLETFEL test devices on silicon base wafers pre-fabricated with reflecting micro-structures, and with TiW and PolySi base electrode materials.

SPICE modelling of the mmLETFEL test devices and optimisation of the theoretical model, with the inclusion of the TiW and PolySi base electrode layers, using SmartSpice of the Virtual Wafer Fabrication (VWF) software from Silvaco International.

SPICE modelling of the various high-voltage drivers, which technologies and SPICE model parameters have been obtained from various fabrication houses, e.g. Holtek, UMC, Supertex, and Alcatel Mietec.

Electrical Characterisation of the selected Alcatel Mietec driver test die, obtained via EuroPractice, using the TECAP system from Hewlett-Packard in RAL, Oxford.

Optimisation of the SPICE model of the corresponding Alcatel Mietec driver test die obtained via EuroPractice.

SPICE modelling of the integrated mmLETFEL cell, consisting of an individual mmLETFEL test device with its corresponding drive circuitry, utilising the previously optimised model parameters.

Calibration and Optimisation of the dicing parameters for the Sola Basic Tempress diamond saw system for the dicing operation of mmLETFEL test devices.

Calibration and Optimisation of the wire-bonding parameters for the K&S wedge-bonder system for the wire-bonding operation of mmLETFEL test devices onto chip-carriers.

# **Table of Contents**

| Abstract                      | ii    |

|-------------------------------|-------|

|                               |       |

| Acknowledgements              | iii   |

| Publications                  | ν     |

| Statement of Work             | vi    |

| Table of Contents             | vii   |

| List of Equations             | xi    |

| List of Figures               | xii   |

| List of Plots                 | xiv   |

| List of Tables                | xv    |

| List of Abbreviations         | xvii  |

| List of Symbols               | xix   |

| List of Units                 | xxi   |

| List of Constants & Variables | xxii  |

| List of References            | xxv   |

| List of Appendix              | xxxii |

# <u>Chapter 1</u>

# Introduction

| 1.1 | Review of Electrophotographic Printing                                   |                                                           |      |  |  |

|-----|--------------------------------------------------------------------------|-----------------------------------------------------------|------|--|--|

|     | 1.1.1                                                                    | Background                                                | 1-3  |  |  |

|     | 1.1.2                                                                    | Electrophotographic Printing Process                      | 1-5  |  |  |

|     | 1.1.3                                                                    | Photoreceptors                                            | 1-7  |  |  |

|     | 1.1.4                                                                    | Light Sources                                             | 1-8  |  |  |

| 1.2 | Review of Alternating Current Thin-Film Electroluminescent Devices       |                                                           |      |  |  |

|     | 1.2.1                                                                    | Introduction                                              | 1-10 |  |  |

|     | 1.2.2                                                                    | Previous Work on ACTFEL devices as image bar arrays       | 1-13 |  |  |

|     | 1.2.3                                                                    | Current Work on Active Matrix Electroluminescent Displays | 1-14 |  |  |

| 1.3 | <b>Review of Laterally-Emitting Thin-Film Electroluminescent Devices</b> |                                                           |      |  |  |

|     | 1.3.1                                                                    | Introduction                                              | 1-15 |  |  |

|     | 1.3.2                                                                    | Previous Work on mmLETFEL linear-array devices            | 1-18 |  |  |

|     |                                                                          |                                                           |      |  |  |

| 1.4 Overview |

|--------------|

|--------------|

| 1.4.1 | Objectiv                      | ves of the Investigation       | 1-19 |

|-------|-------------------------------|--------------------------------|------|

| 1.4.2 | .2 Preliminary Investigations |                                | 1-23 |

|       | 1.4.2.1                       | Photoreceptor Measurements     |      |

|       | 1.4.2.2                       | Electrode Materials Properties |      |

| 1.4.3 | Summar                        | ry of the Thesis               | 1-27 |

|       |                               |                                |      |

# <u>Chapter 2</u>

| <b>Fabrication</b> | of                | mmLE | TFEL | Test D | evices |

|--------------------|-------------------|------|------|--------|--------|

|                    | Territoria Canada |      |      |        |        |

| 2.1 | Intro              | duction                                                             | 2-1  |  |  |  |

|-----|--------------------|---------------------------------------------------------------------|------|--|--|--|

| 2.2 | Depos              | Deposition Techniques                                               |      |  |  |  |

|     | 2.2.1              | Sputtering                                                          | 2-3  |  |  |  |

|     |                    | 2.2.1.1 D.C. Sputtering                                             |      |  |  |  |

|     |                    | 2.2.1.2 R.F. Sputtering                                             |      |  |  |  |

|     |                    | 2.2.1.3 Magnetron Sputtering                                        |      |  |  |  |

|     | 2.2.2              | Chemical Vapor Deposition (CVD)                                     | 2-7  |  |  |  |

|     |                    | 2.2.2.1 Low Pressure Chemical Vapor Deposition (LPCVD)              |      |  |  |  |

|     |                    | 2.2.2.2 Plasma-Enhanced Chemical Vapor Deposition (PECVD)           |      |  |  |  |

| 2.3 | Etching Techniques |                                                                     |      |  |  |  |

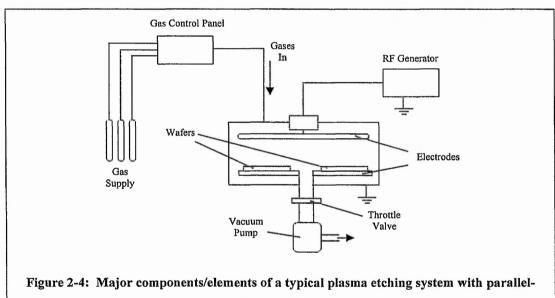

|     | 2.3.1              | Plasma Etching                                                      | 2-10 |  |  |  |

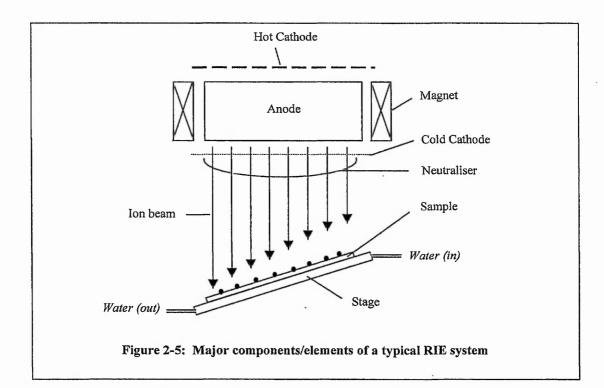

|     | 2.3.2              | Reactive Ion Etching                                                | 2-11 |  |  |  |

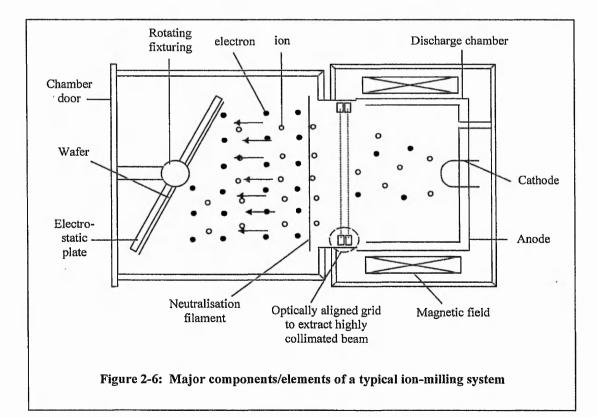

|     | 2.3.3              | Ion Beam Milling                                                    | 2-12 |  |  |  |

| 2.4 | Proc               | ess Conditions for mmLETFEL Fabrication                             | 2-13 |  |  |  |

|     | 2.4.1              | Fabrication of the Base Electrode                                   | 2-15 |  |  |  |

|     |                    | 2.4.1.1 Insulating layer: Thermal Oxide (T <sub>OX</sub> )          |      |  |  |  |

|     |                    | 2.4.1.2 Base Electrode: PolySilicon (PolySi)                        |      |  |  |  |

|     |                    | 2.4.1.3 Base Electrode: Titanium/Tungsten (TiW)                     |      |  |  |  |

|     | 2.4.2              | Fabrication of the Micro-Mirror Structure                           | 2-17 |  |  |  |

|     |                    | 2.4.2.1 Micro-mirror Structure: Silicon Dioxide (SiO <sub>2</sub> ) |      |  |  |  |

|     | 2.4.3              | Fabrication of TFEL Devices                                         | 2-19 |  |  |  |

|     |                    | 2.4.3.1 Phosphor: Zinc Sulphide doped with Manganese (ZnS:Mn)       |      |  |  |  |

|     |                    | 2.4.3.2 Insulator: Yttrium Oxide $(Y_2O_3)$                         |      |  |  |  |

|     |                    | 2.4.3.3 Insulator: Silicon Nitride (Si <sub>3</sub> $N_4$ )         |      |  |  |  |

State ...

. . .

| 2-21 |

|------|

|      |

|      |

| 2-23 |

| 2-26 |

| 2-27 |

| 2-32 |

| 2-33 |

|      |

| Chapter | 3 |

|---------|---|

|         |   |

# Characterisation of mmLETFEL Test Devices

| 3.1 | Intro  | luction                                                        | 3-1  |

|-----|--------|----------------------------------------------------------------|------|

| 3.2 | mmL    | ETFEL Test Device Structures                                   | 3-3  |

| 3.3 | mmL    | ETFEL Measurement and Characterisation Techniques              | 3-7  |

|     | 3.3.1  | Optical Characterisation                                       | 3-9  |

|     | 3.3.2  | Electrical Characterisation                                    | 3-12 |

| 3.4 | mmL    | ETFEL Test Device Parameters                                   | 3-15 |

| 3.5 | mmL    | ETFEL Electro-Optical Characteristics                          | 3-17 |

|     | 3.5.1. | mmLETFEL test devices under different drive conditions         | 3-22 |

|     | 3.5.2. | mmLETFEL test devices with varying features                    | 3-24 |

|     |        | 3.5.2.1 Active Material Length and Sidewall Widths             |      |

|     |        | 3.5.2.2 Aperture and Micro-Mirror Widths                       |      |

|     | 3.5.3  | mmLETFEL test devices with different base electrodes           | 3-30 |

|     | 3.5.4  | mmLETFEL test devices with different insulators                | 3-34 |

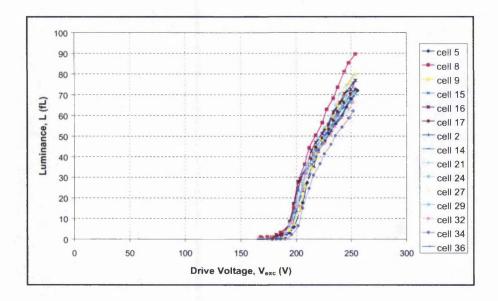

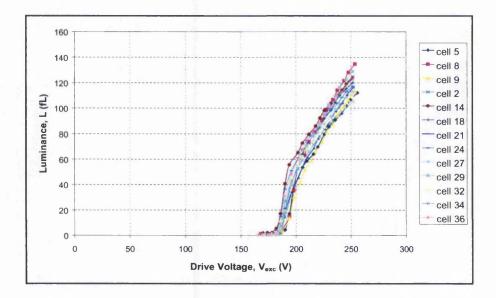

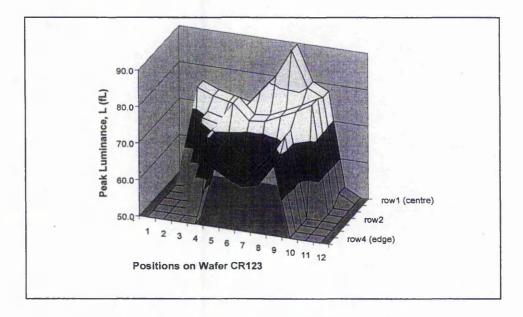

|     | 3.5.5  | Reproducibility of mmLETFEL test devices in terms of luminance | 3-38 |

| 3.6 | Conc   | lusion                                                         | 3-43 |

and the second of the burner of the second of the

### Chapter 4

# Characterisation and SPICE Modelling of High-Voltage MOSFETs

| 4.1 | Introduction                                                | 4-1  |

|-----|-------------------------------------------------------------|------|

| 4.2 | History of SPICE                                            | 4-2  |

| 4.3 | SPICE Models of Commercial Drivers                          | 4-4  |

| 4.4 | Electrical Characterisation of Alcatel NDMOSHV Test Devices | 4-9  |

| 4.5 | SPICE Modelling of Alcatel NDMOSHV Test Devices             | 4-11 |

| 4.6 | Conclusion                                                  | 4-15 |

### <u>Chapter 5</u>

# SPICE Modeling of mmLETFEL Test Devices and the Integrated mmLETFEL Device

| 5.1 | .1 Introduction      |                                       |      |  |

|-----|----------------------|---------------------------------------|------|--|

| 5.2 | mmLETFEL SPICE Model |                                       |      |  |

|     | 5.2.1                | mmLETFEL Device Structure             | 5-2  |  |

|     | 5.2.2                | mmLETFEL Equivalent Circuit           | 5-3  |  |

|     | 5.2.3                | mmLETFEL Device Electrical Parameters | 5-4  |  |

|     | 5.2.4                | mmLETFEL Simulations                  | 5-7  |  |

| 5.3 | OEIC                 | C Model Circuit                       | 5-10 |  |

| 5.4 | Conc                 | lusion                                | 5-16 |  |

### Chapter 6

# Final Conclusions

| 6.1 | Summary of Thesis                                 | 6-1  |

|-----|---------------------------------------------------|------|

| 6.2 | Achievements                                      | 6-2  |

| 6.3 | Latest Developments of mmLETFEL Devices           | 6-5  |

| 6.4 | Proposed Processing Sequence for OEIC Development | 6-8  |

| 6.5 | Future Work                                       | 6-10 |

x

# List of Equations

| Equation 1-1  | Length of a page                                                                                                            |

|---------------|-----------------------------------------------------------------------------------------------------------------------------|

| Equation 1-2  | Speed of the drum in p.p.m.                                                                                                 |

| Equation 1-3  | Sensitivity/Gain of a photoreceptor                                                                                         |

| Equation 3-1  | Equation used for correction of measured luminance value                                                                    |

| Equation 3-2  | Multiplying factor, K                                                                                                       |

| Equation 3-3  | Charge expression derived from employing sense capacitor                                                                    |

| Equation 3-4  | Current expression derived from Equation 3-3                                                                                |

| Equation 3-5  | Current expression derived from Equation 3-3 (if series resistor was used)                                                  |

| Equation 3-6  | Current expression derived from employing sense resistor                                                                    |

| Equation 3-7  | Capacitance expression derived from the charge expression                                                                   |

| Equation 3-8  | Capacitance expression derived from the current expression                                                                  |

| Equation 3-9  | Capacitance expression derived from structure parameters                                                                    |

| Equation 3-10 | Capacitance expression derived from structure parameters                                                                    |

| Equation 3-11 | Equation depicting slope C <sub>off</sub> (total capacitance before turn-on)                                                |

| Equation 3-12 | Equation depicting slope C <sub>off</sub> (total capacitance before turn-on)                                                |

| Equation 3-13 | Equation depicting slope C <sub>on</sub> (total capacitance after turn-on)                                                  |

| Equation 3-14 | Equation for C <sub>off</sub> in terms of phosphor and insulator capacitances                                               |

| Equation 3-15 | Equation for C <sub>on</sub> in terms of phosphor and insulator capacitances                                                |

| Equation 3-16 | Equation for phosphor capacitance, C <sub>p</sub> , in terms of C <sub>off</sub> and C <sub>on</sub>                        |

| Equation 3-17 | Equation for insulator capacitances, C <sub>i1</sub> and C <sub>i2</sub> , in terms of C <sub>off</sub> and C <sub>on</sub> |

| Equation 3-18 | Equation depicting slope Con in terms of phosphor threshold voltage, V <sub>th, ph</sub>                                    |

| Equation 3-19 | Equation for E <sub>in</sub> , input energy density                                                                         |

| Equation 3-20 | Equation for E <sub>in</sub> , input energy density                                                                         |

| Equation 3-21 | Equation for P <sub>in</sub> , input power density                                                                          |

| Equation 3-22 | Equation for $\eta_{eff}$ , luminous efficiency                                                                             |

| Equation 3-23 | Equation for $\eta_{eff}$ , luminous efficiency (at specified voltage, $(V_{th} + V_{m1})$ )                                |

| Equation 3-24 | Interface boundary conditions defined by Maxwell equations                                                                  |

| Equation 3-25 | Relationship between voltages across the insulating and phosphor layers                                                     |

| Equation 3-26 | Fraction of voltage across the phosphor layer in terms of the peak voltage                                                  |

| Equation 3-27 | Equation for the electric field of an insulating layer                                                                      |

| Equation 4-1  | Error margin/tolerance (%) for measured-simulated values                                                                    |

| Equation 5-1  | Capacitance of a layer                                                                                                      |

| Equation 5-2  | Resistance of a layer                                                                                                       |

| Equation 5-3  | Insulator capacitance of a layer at a given resolution                                                                      |

| Equation 5-4  | Phosphor capacitance of a layer at a given resolution                                                                       |

| Equation 5-5  | Insulator resistance of a layer at a given resolution                                                                       |

| Equation 5-6  | Phosphor resistance of a layer at a given resolution                                                                        |

| Equation 5-7  | Resistance of a layer using sheet resistance                                                                                |

| Equation 5-8  | Breakdown voltage for zener diodes in terms of Qth                                                                          |

| Equation 5-9  | Breakdown voltage for zener diodes in terms of V <sub>th</sub>                                                              |

| Equation 5-10 | Breakdown voltage for zener diodes in terms of C <sub>p</sub> and C <sub>i</sub>                                            |

C.VP.

# List of Figures

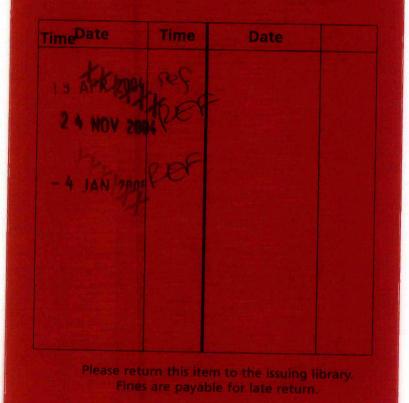

| Figure 1-1  | Six distinct steps of the electrophotographic printing process                |

|-------------|-------------------------------------------------------------------------------|

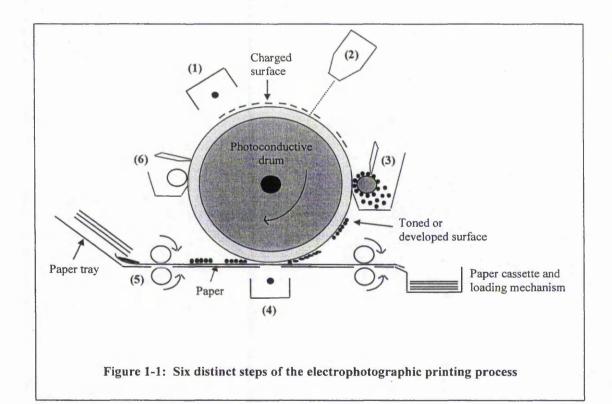

| Figure 1-2  | Structure of a double-insulating-layer type ACTFEL device                     |

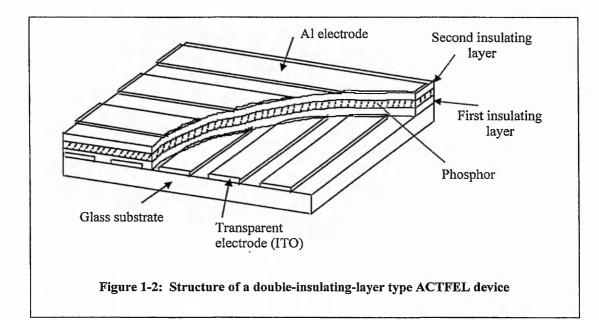

| Figure 1-3  | Energy-band diagram of the double-insulating-layer type ACTFEL device         |

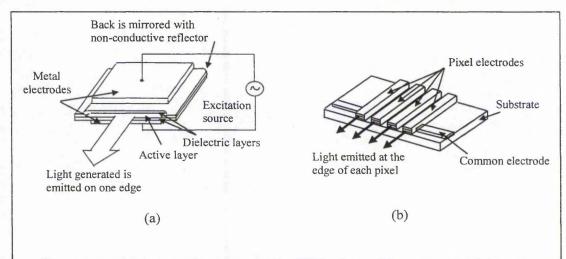

| Figure 1-4  | (a) Schematic illustration of the TFEL edge-emitter concept                   |

| -           | (b) Schematic arrangement of an edge-emitter array                            |

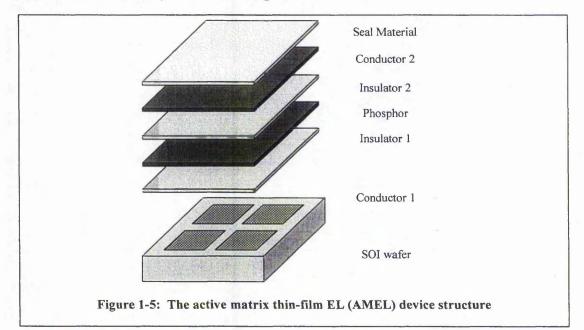

| Figure 1-5  | The active matrix thin-film EL (AMEL) device structure                        |

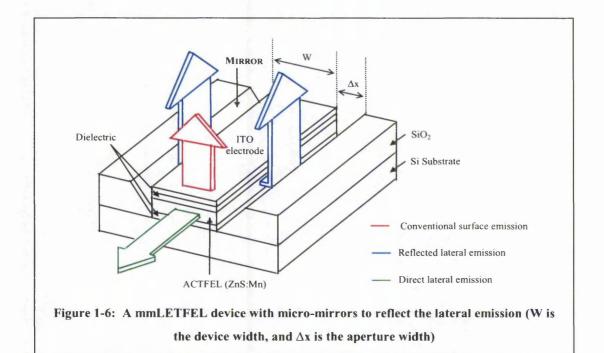

| Figure 1-6  | A mmLETFEL device with micro-mirrors to reflect the lateral emission (W       |

| -           | is the device width, and $\Delta x$ is the aperture width)                    |

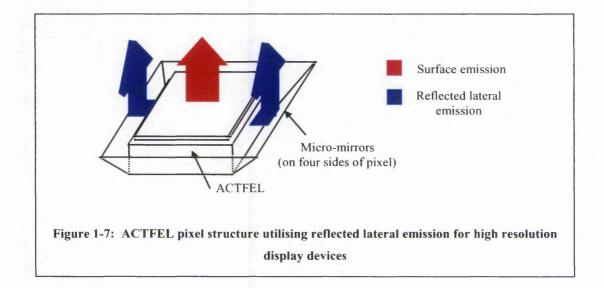

| Figure 1-7  | ACTFEL pixel structure utilising reflected lateral emission for high          |

| 0           | resolution display devices                                                    |

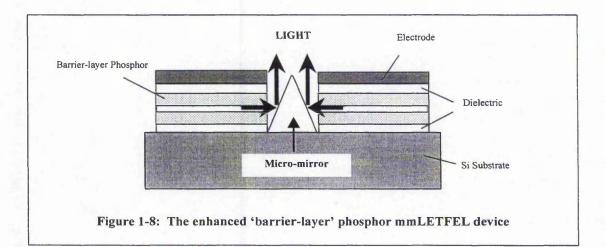

| Figure 1-8  | The enhanced 'barrier-layer' phosphor mmLETFEL device                         |

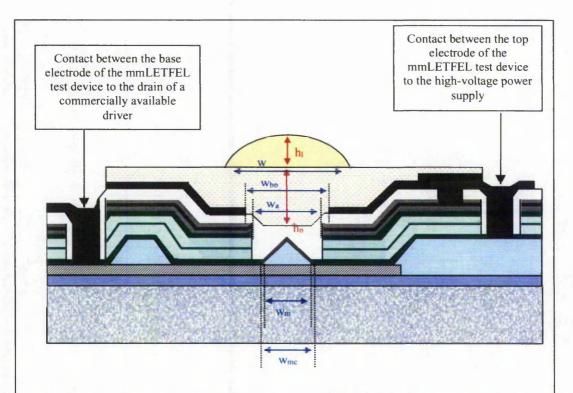

| Figure 1-9  | Cross-sectional view of a typical mmLETFEL test device structure, with        |

|             | indications to the top and bottom electrode contacts                          |

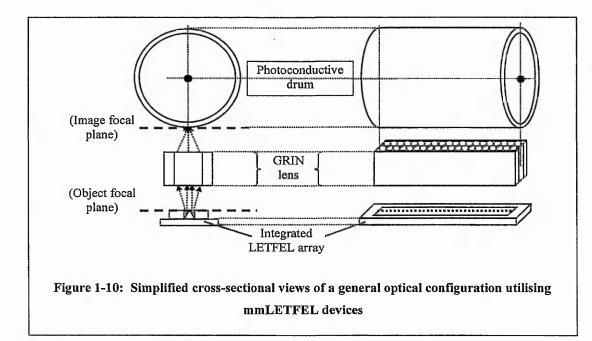

| Figure 1-10 | Simplified cross-sectional views of a general optical configuration utilising |

|             | mmLETFEL devices                                                              |

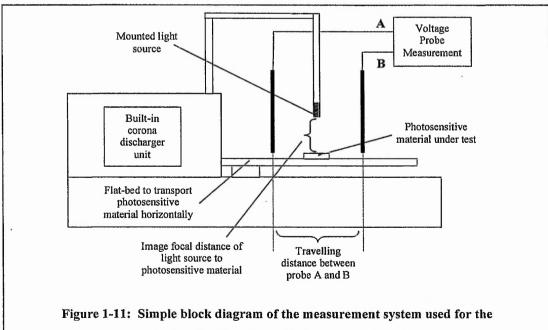

| Figure 1-11 | Simple block diagram of the measurement system used for the                   |

|             | photoconductive drum discharge experiment                                     |

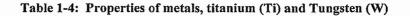

| Figure 2-1  | General features of a typical sputtering system                               |

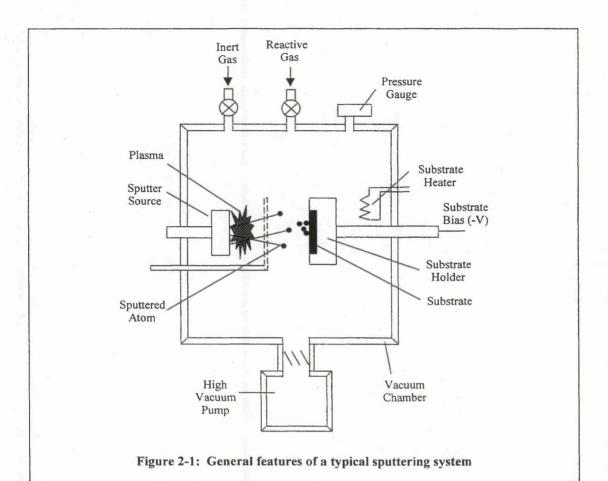

| Figure 2-2  | Cross-sectional view of a typical planar magnetron sputter source             |

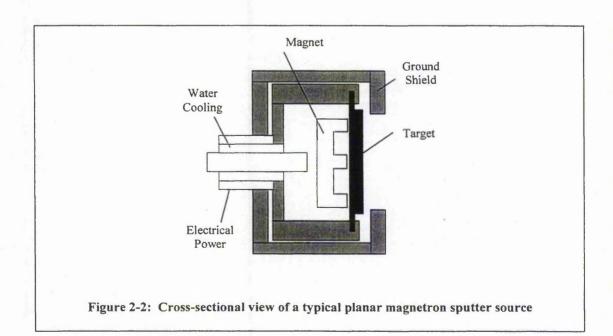

| Figure 2-3  | Major components/elements of a typical PECVD reactor with conventional        |

| U U         | parallel-plate electrode                                                      |

| Figure 2-4  | Major components/elements of a typical plasma etching system with             |

| -           | parallel-plate electrodes                                                     |

| Figure 2-5  | Major components/elements of a typical RIE system                             |

| Figure 2-6  | Major components/elements of a typical ion-milling system                     |

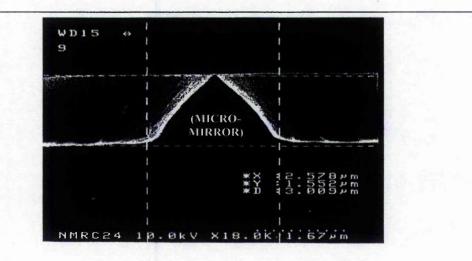

| Figure 2-7  | A cross-sectional view of the successful formation of a micro-mirror          |

|             | structure being fabricated at NMRC                                            |

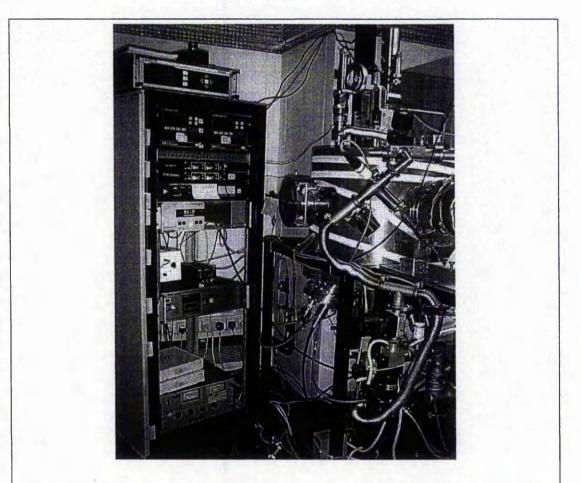

| Figure 2-8  | Sputtering system used for deposition of phosphor and insulator thin-films    |

|             | of mmLETFEL test devices at TNTU                                              |

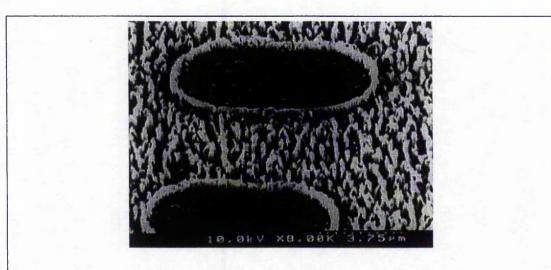

| Figure 2-9  | Illustrating the protruding "spikes" occurring at the Al layer                |

| Figure 2-10 | Photoresist spinner used for resist coating of thin-films at TNTU             |

| Figure 2-11 | Mask aligner used for thin-film patterning via u-v exposure at TNTU           |

| Figure 2-12 | Platform used for development of photoresist after u-v exposure at TNTU       |

| Figure 2-13 | Scan profiler used for determining thickness of thin-films at TNTU            |

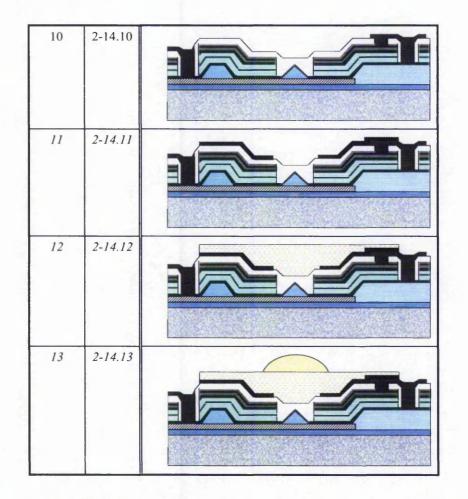

| Figure 2-14 | Graphical illustration of the full processing sequence of a mmLETFEL          |

|             | device (Figure 2-14.1 to Figure 2-14.13)                                      |

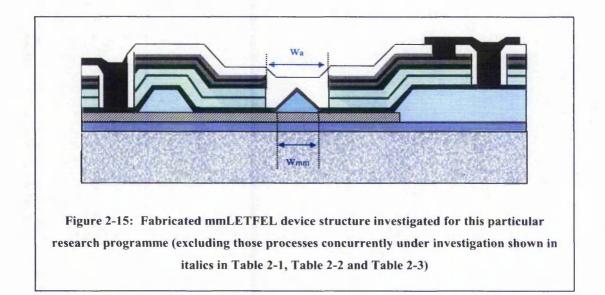

| Figure 2-15 | Fabricated mmLETFEL device structure investigated for this particular         |

|             | research programme                                                            |

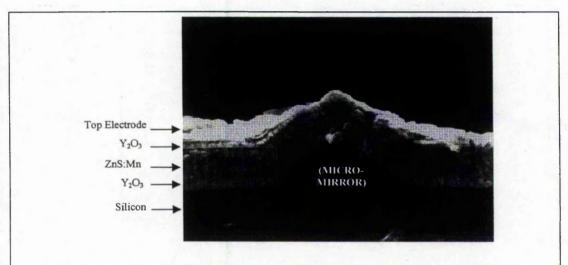

| Figure 2-16 | A conventional mmLETFEL device with non-etched aperture profile               |

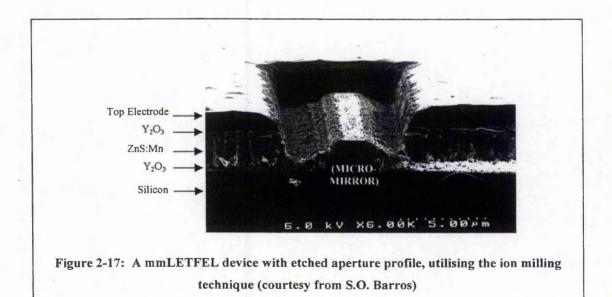

| Figure 2-17 | A mmLETFEL device with etched aperture profile, utilising the ion milling     |

|             | technique (courtesy from S.O. Barros)                                         |

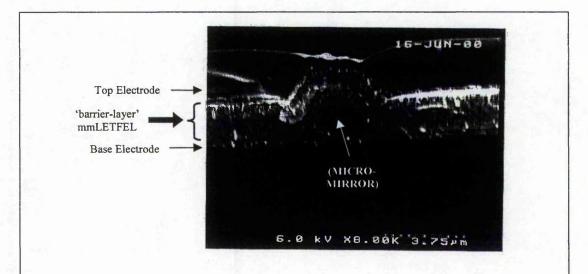

| Figure 2-18 | mmLETFEL test device primarily utilised in this investigation - containing    |

|             | fabricated base electrode and 'barrier-layer' mmLETFEL structure              |

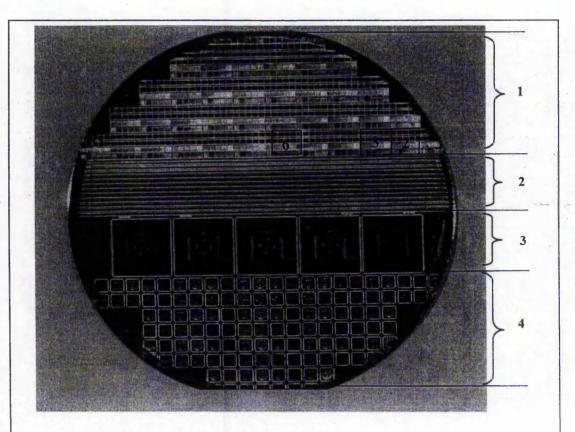

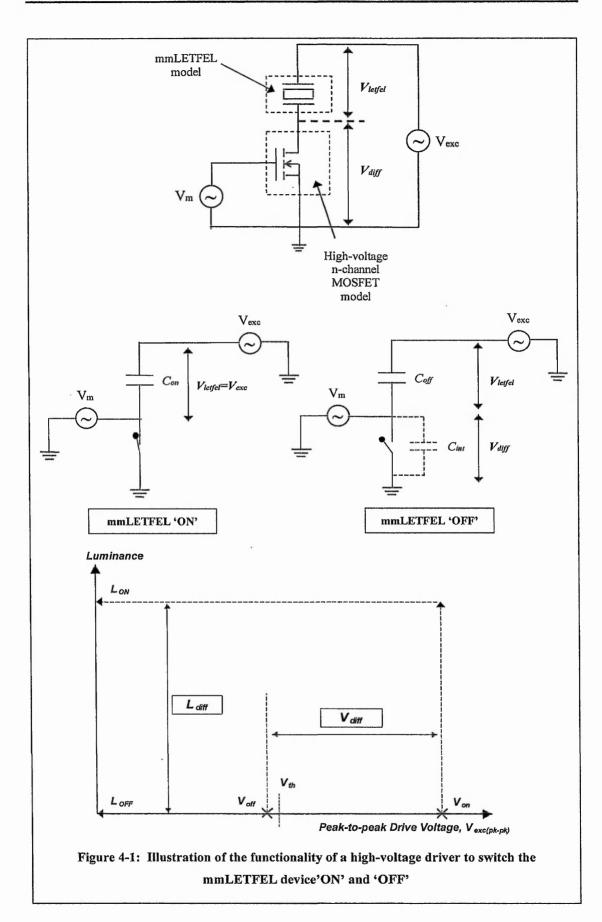

| Figure 2-19 | A test wafer illustrating the mask set used for the fabrication of mmLETFEL   |

|             | devices in this investigation                                                 |

xii

S .. . .

# List of Figures (Continued)

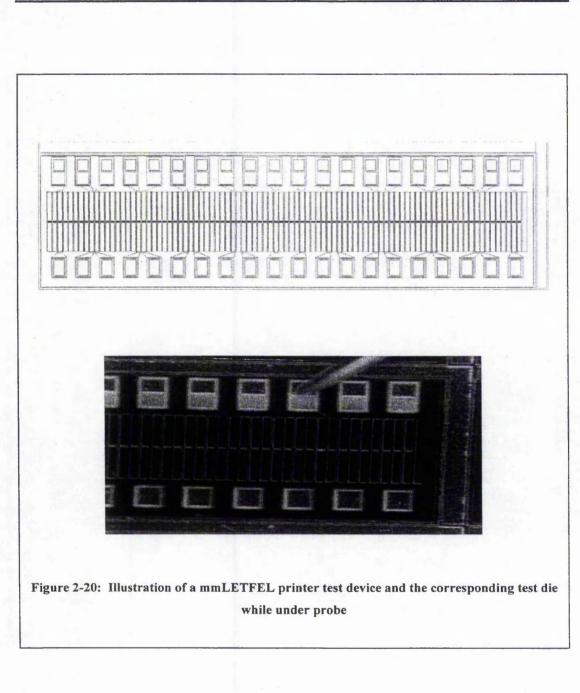

| Figure 2-20            | Illustration of a mmLETFEL printer test device and the corresponding test die while under probe                                                            |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

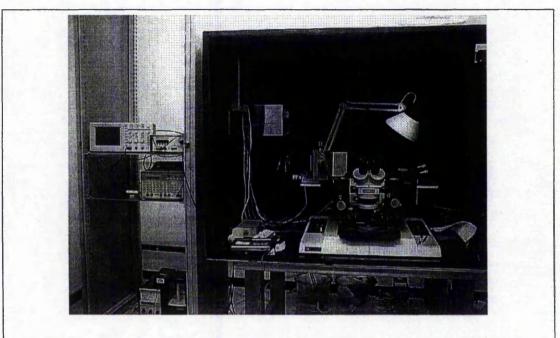

| Figure 3-1             | The main wafer prober station used for characterisation of mmLETFEL test devices                                                                           |

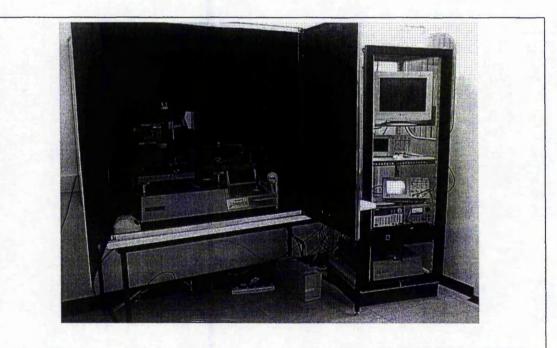

| Figure 3-2             | The secondary wafer prober station used for characterisation of mmLETFEL test devices                                                                      |

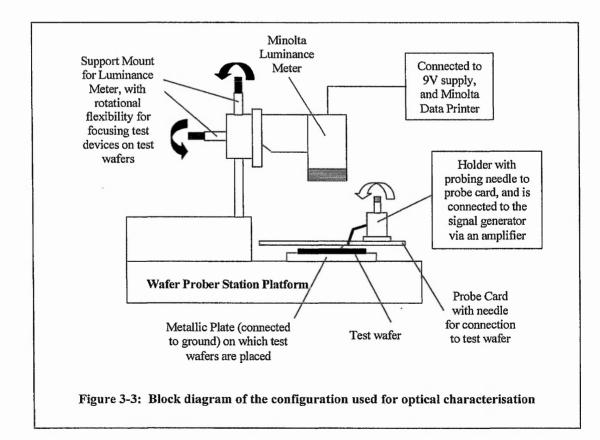

| Figure 3-3             | Block diagram of the configuration used for optical characterisation                                                                                       |

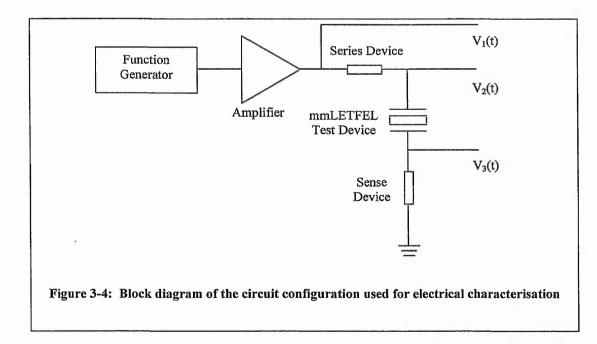

| Figure 3-4             | Block diagram of the circuit configuration used for electrical characterisation                                                                            |

| Figure 3-5             | System used for evaporation of Al material at TNTU                                                                                                         |

| Figure 3-6             | Wafer prober station used primarily for C-V characterisation of thin-films                                                                                 |

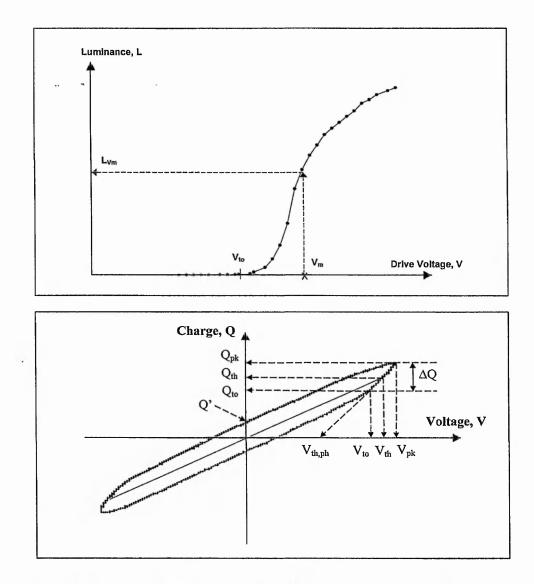

| Figure 3-7             | Typical L-V and Q-V characteristics obtained for a mmLETFEL test device                                                                                    |

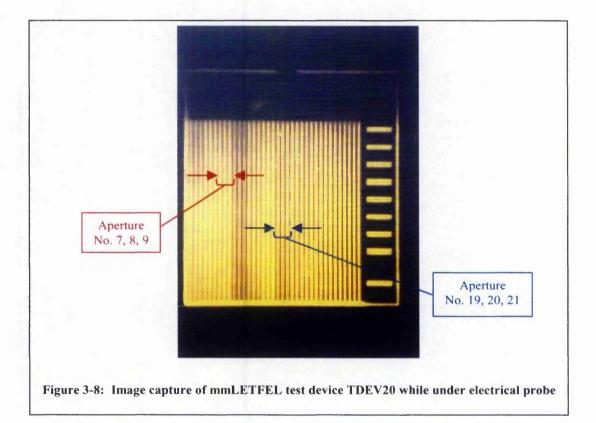

| Figure 3-8             | Image capture of mmLETFEL test device TDEV20 while under electrical probe                                                                                  |

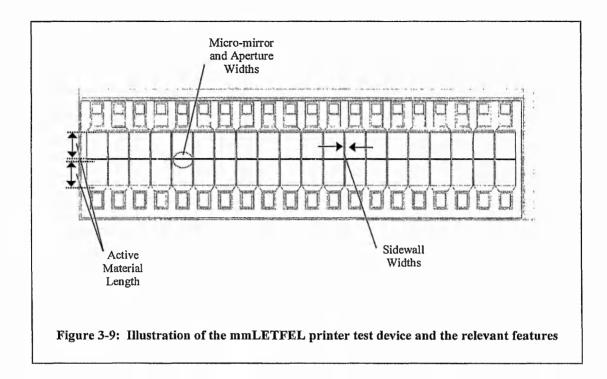

| Figure 3-9             | Illustration of the mmLETFEL printer test device and the relevant features                                                                                 |

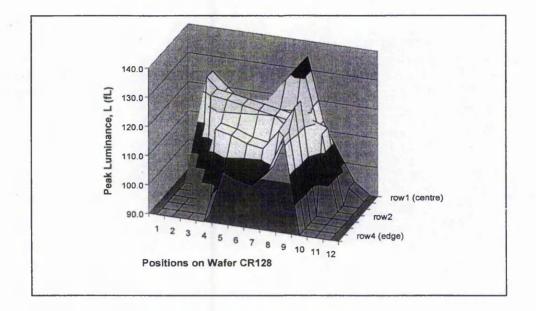

| Figure 4-1             | Illustration of the functionality of a high-voltage driver to switch the mmLETFEL device'ON' and 'OFF'                                                     |

| Figure 4-2             | Schematic of the Alcatel Mietec test die                                                                                                                   |

| Figure 4-3             | Schematic of the wire-bonded Alcatel Mietec test die on a chip carrier                                                                                     |

| Figure 4-4             | Block diagram illustrating the TECAP system used for electrical characterisation of Alcatel test die                                                       |

| Figure 4-5             | The equivalent circuit of the Alcatel Mietec NDMOSHV model used and optimised for SPICE modelling                                                          |

| Figure 5-1             | Schematic diagram depicting the mmLETFEL basic device structure to be<br>used for derivation of its equivalent circuit and subsequent SPICE<br>simulations |

| Figure 5-2             | Equivalent circuit used for SPICE simulation of a mmLETFEL pixel                                                                                           |

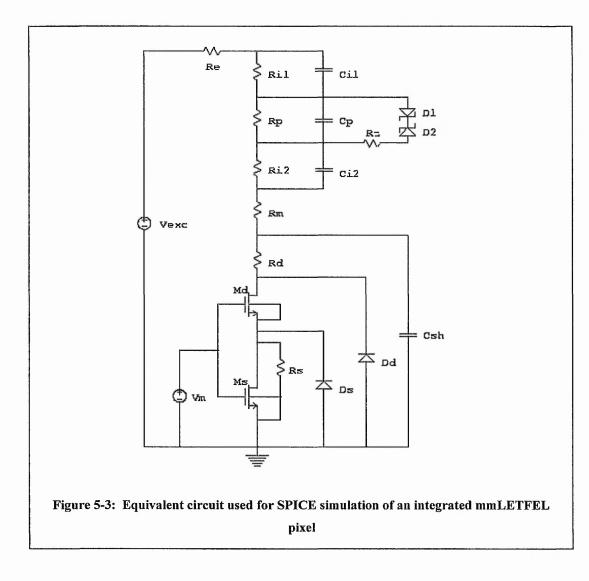

| Figure 5-3             | Equivalent circuit used for SPICE simulation of an integrated mmLETFEL pixel pixel                                                                         |

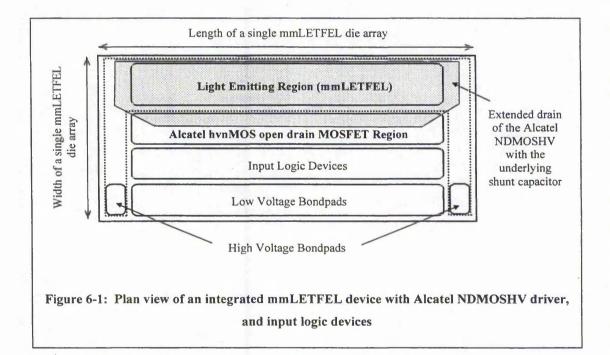

| Figure 6-1             | Plan view of an integrated mmLETFEL device with Alcatel NDMOSHV driver, and input logic devices                                                            |

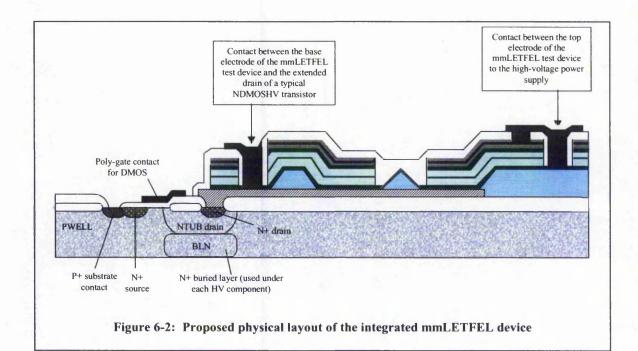

| Figure 6-2             | Proposed physical layout of the integrated mmLETFEL device                                                                                                 |

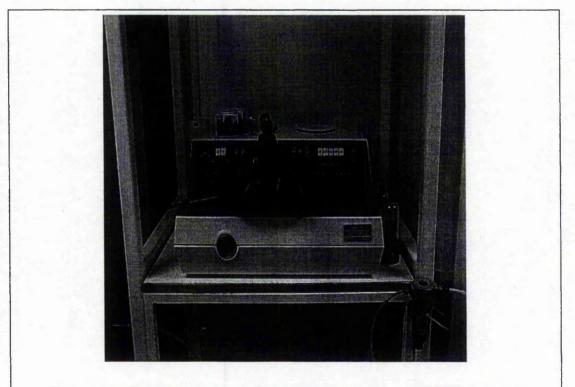

| Figure B1-1            | Diamond saw machine utilised for dicing operation                                                                                                          |

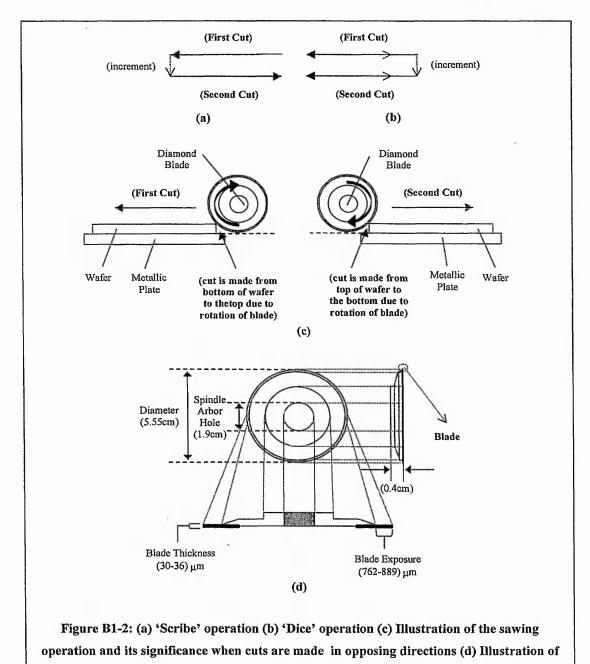

| Figure B1-2            | Illustration of dicing operation                                                                                                                           |

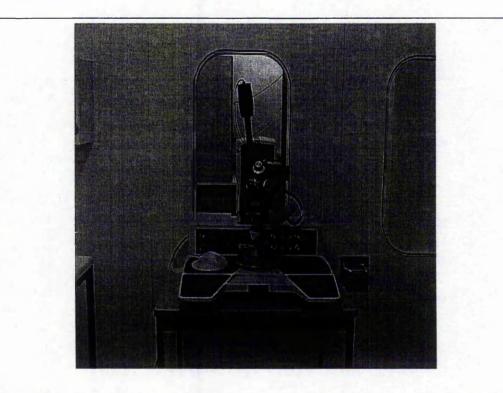

| Figure B3-1            | Wedge-bonder utilised for wire-bonding operation                                                                                                           |

| Figure B3-2            | Illustration of a wire-bonded HMD optics mount                                                                                                             |

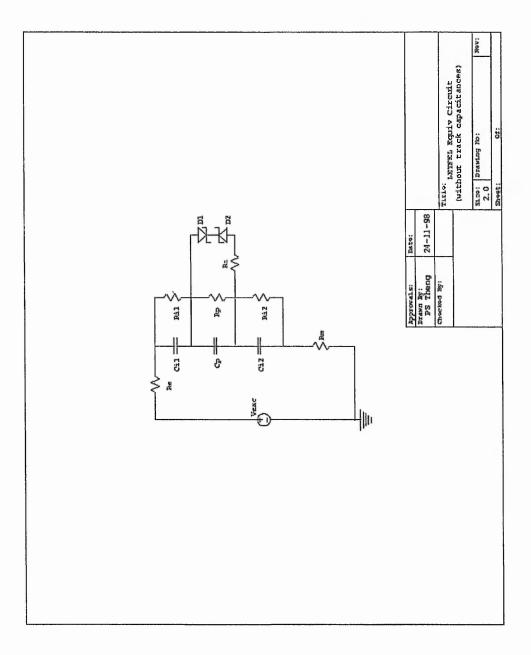

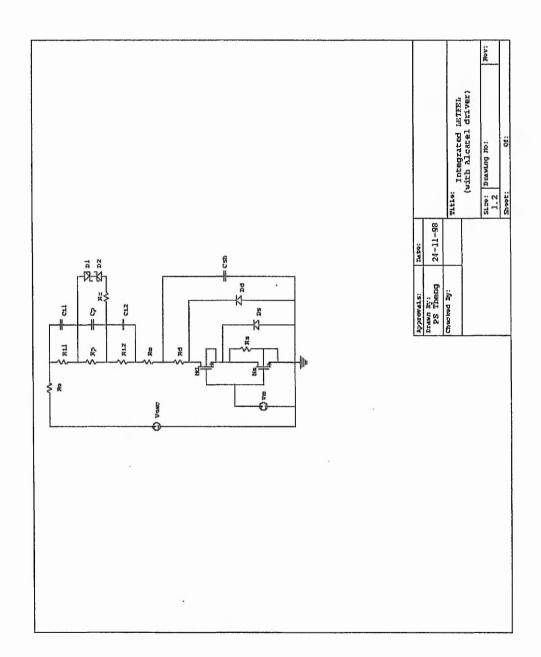

| Figure E1<br>Figure E2 | Circuit diagram of mmLETFEL device used in SmartSPICE simulations<br>Circuit diagram of integrated mmLETFEL device used in SmartSPICE                      |

| 0                      | simulations                                                                                                                                                |

# **List of Plots**

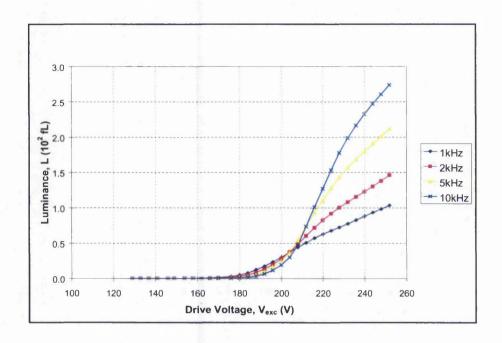

- Plot 3-1 mmLETFEL test device driven by a sinusoidal waveform at 1, 2, 5, and 10kHz

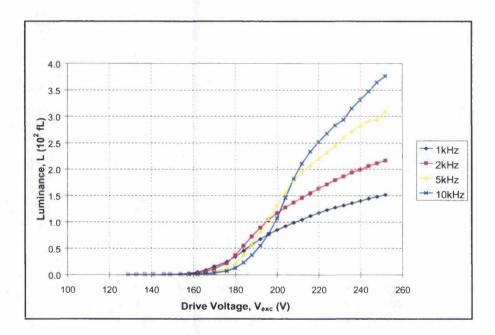

- Plot 3-2 mmLETFEL test device driven by a square waveform at 1, 2, 5 and 10kHz

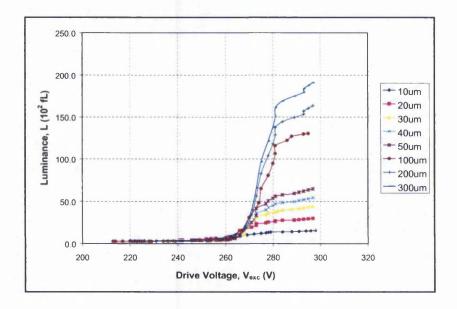

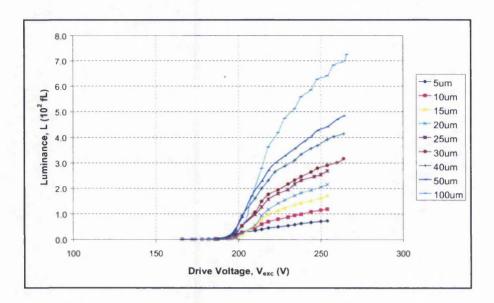

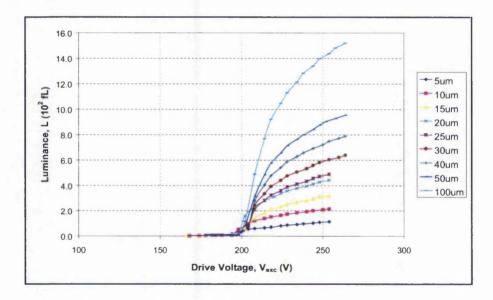

- Plot 3-3 Comparative L-V characteristics of mmLETFEL test devices TDEV01-TDEV08

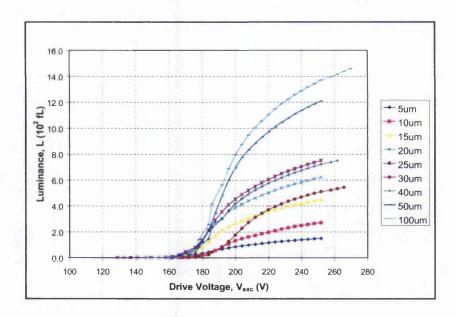

- Plot 3-4 Comparative L-V characteristics of mmLETFEL test devices TDEV11-TDEV19

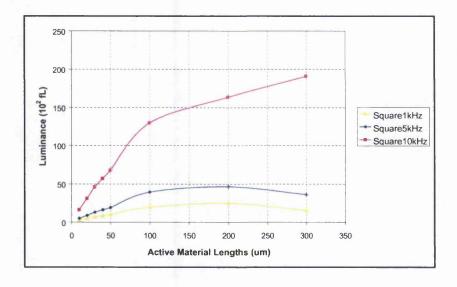

- Plot 3-5 Luminance versus Active Material Lengths of mmLETFEL test devices

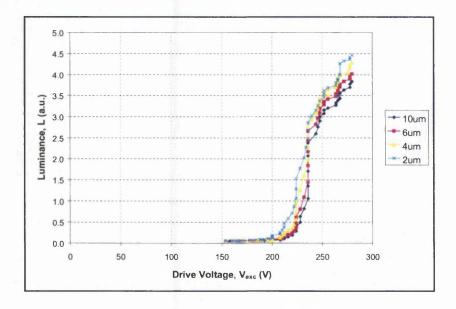

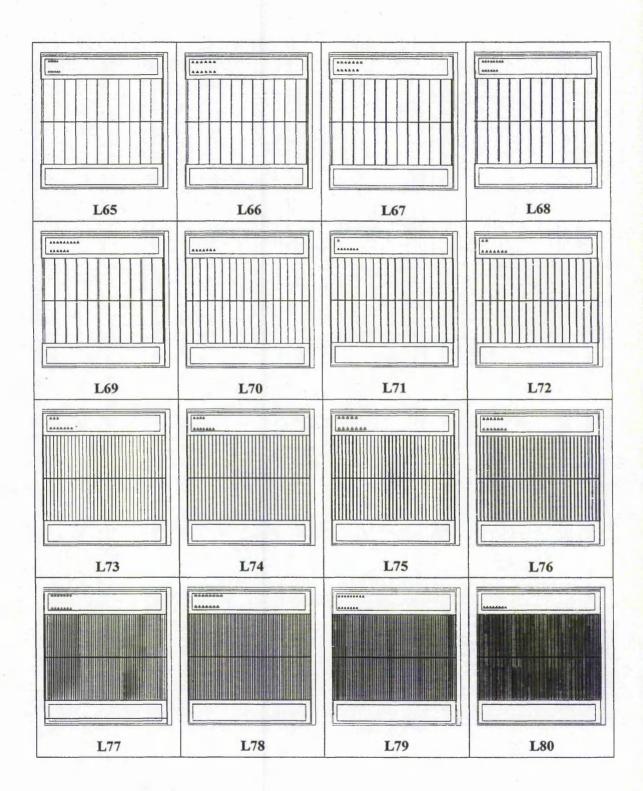

- Plot 3-6 Comparative L-V characteristics of mmLETFEL test devices L65-L80

- (representation for differing sidewall widths at various resolutions)

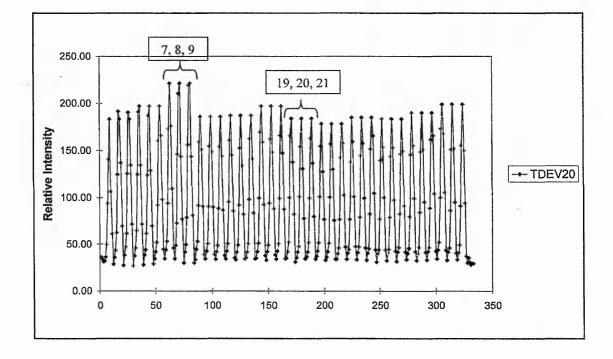

- Plot 3-7 Image profile of mmLETFEL test device TDEV20

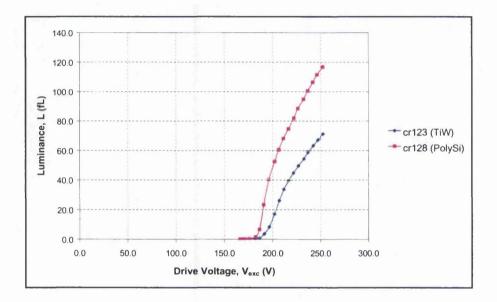

- Plot 3-8 Comparative L-V characteristics of mmLETFEL TDEV11 grown with PolySi and TiW materials as base electrodes (Y<sub>2</sub>O<sub>3</sub> as insulators)

- Plot 3-9 Comparative Q-V characteristics of mmLETFEL TDEV11 grown with PolySi and TiW materials as base electrodes (Y<sub>2</sub>O<sub>3</sub> as insulators)

- Plot 3-10 Comparative I-V characteristics of mmLETFEL TDEV11 grown with PolySi and TiW materials as base electrodes (Y<sub>2</sub>O<sub>3</sub> as insulators)

- Plot 3-11 Comparative L-V characteristics of mmLETFEL TDEV11 grown with Y<sub>2</sub>O<sub>3</sub> and Si<sub>3</sub>N<sub>4</sub> materials as insulators (TiW as base electrodes)

- Plot 3-12 Comparative Q-V characteristics of a mmLETFEL test device grown with  $Y_2O_3$ and  $Si_3N_4$  materials as insulators (TiW as base electrodes)

- Plot 4-1 Average measured-simulated  $I_{ds}$ - $V_{ds}$  characteristics of NDMOSHV test devices (Gate voltages of  $V_{gs}$ =0V-5V at 1V increment)

- Plot 4-2 Average measured-simulated  $I_{ds}$ - $V_{gs}$  characteristics of NDMOSHV test devices (Drain voltage of  $V_{ds}$ =1V)

- Plot 4-3 Average measured-simulated  $I_{ds}$ - $V_{gs}$  characteristics of NDMOSHV test devices (Drain voltage of  $V_{ds}$ =80V)

- Plot 5-1 Q-V characteristics of experimental-simulated results of mmLETFEL TDEV11 from wafer CR123 ( $Y_2O_3$  as insulators and TiW as base electrode)

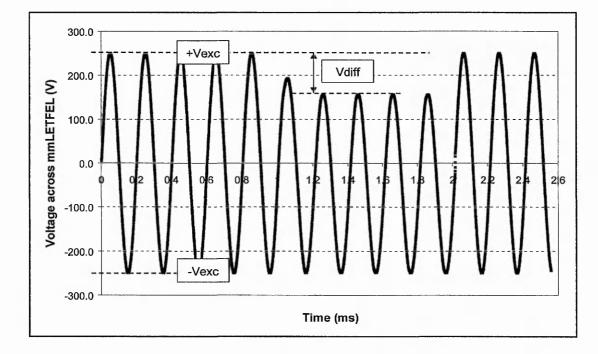

- Plot 5-2 The voltage drop across a mmLETFEL test device (at 600 d.p.i.) vs time

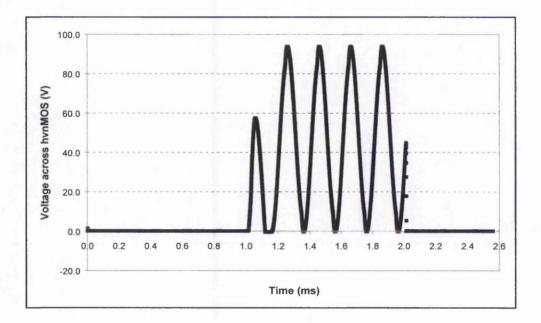

- Plot 5-3 The voltage drop across the NDMOSHV device vs time

# List of Tables

| Table 1-1  | Methods to be employed for optimisation of mmLETFEL's efficiency                                                                                                                                                          |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 1-2  | Description of the layers and denotations of the mmLETFEL device structure                                                                                                                                                |

| Table 1-3  | The travelling time, corresponding drum speed and drum sensitivity are tabulated for the Fuji 9B-003                                                                                                                      |

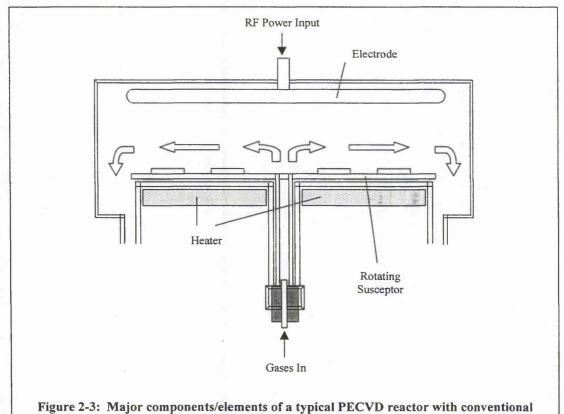

| Table 1-4  | Properties of metals, titanium (Ti) and Tungsten (W)                                                                                                                                                                      |

| Table 2-1  | List of the names and their corresponding material layer of the mask set designed for photolithography of mmLETFEL fabrication                                                                                            |

| Table 2-2  | List of the step-by-step processing route of a mmLETFEL device                                                                                                                                                            |

| Table 2-3  | Graphical illustration of the full processing sequence of a mmLETFEL device (Figure 2-14.1 to Figure 2-14.13)                                                                                                             |

| Table 2-4  | Description of the layers and denotations used in Table 2-3 and Figure 2-15 of the fully fabricated mmLETFEL device structure                                                                                             |

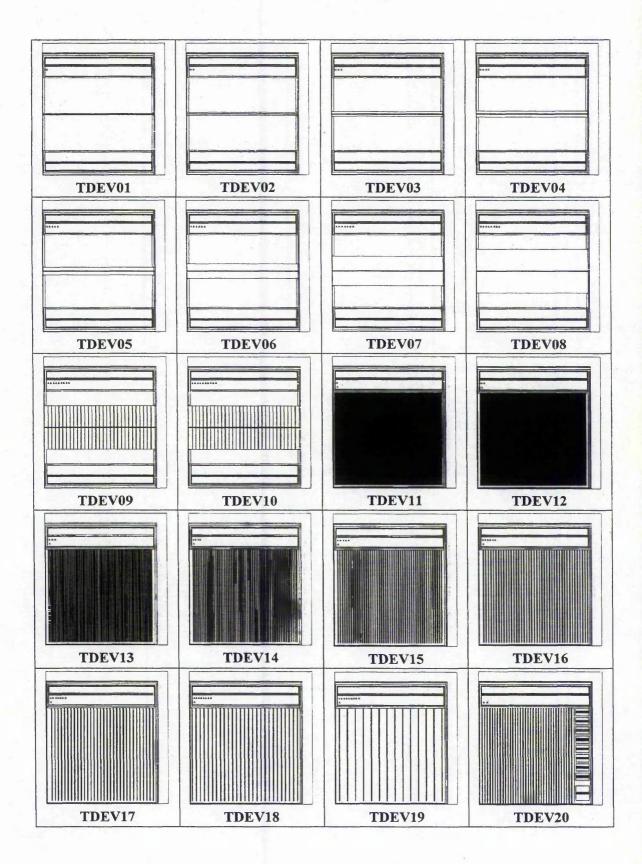

| Table 3-1  | List of the test wafers fabricated and their corresponding descriptions                                                                                                                                                   |

| Table 3-2  | List of characterised mmLETFEL test device structures, their dimensions and graphical illustrations (for L65-L80)                                                                                                         |

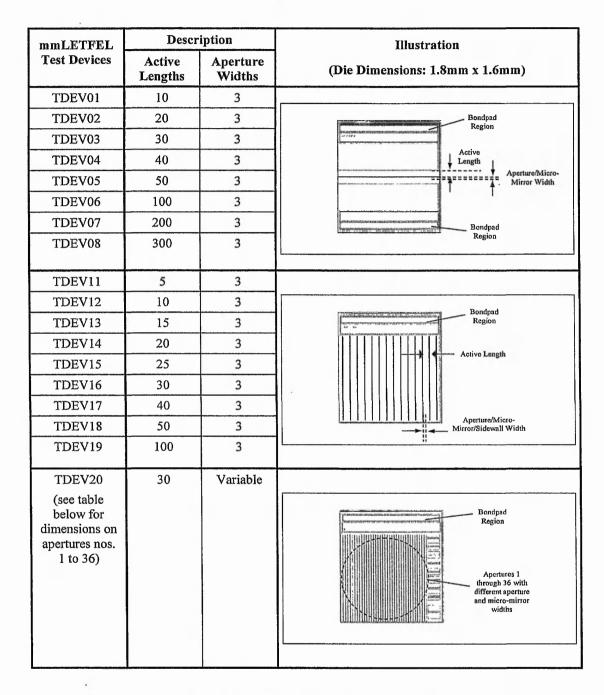

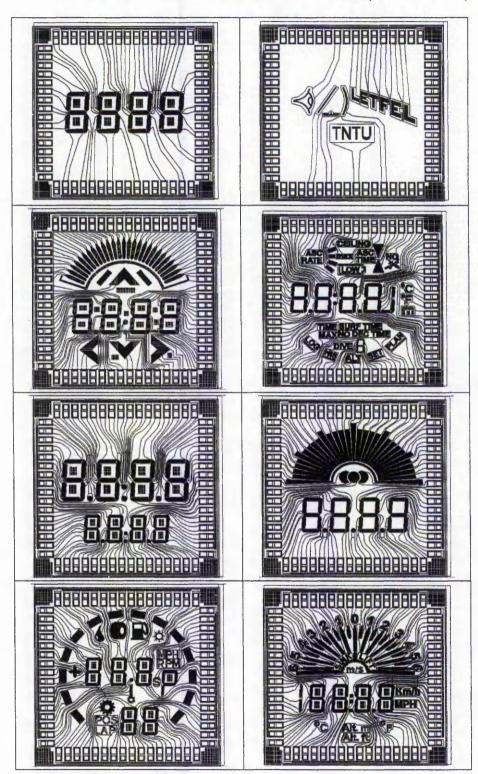

| Table 3-3  | List of characterised mmLETFEL test device structures, their dimensions and graphical illustrations (for TDEV01-08, TDEV11-20)                                                                                            |

| Table 3-4  | Description of mmLETFEL test device TDEV20 (for apertures 1 to 36)                                                                                                                                                        |

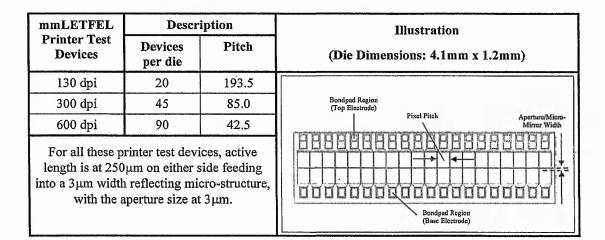

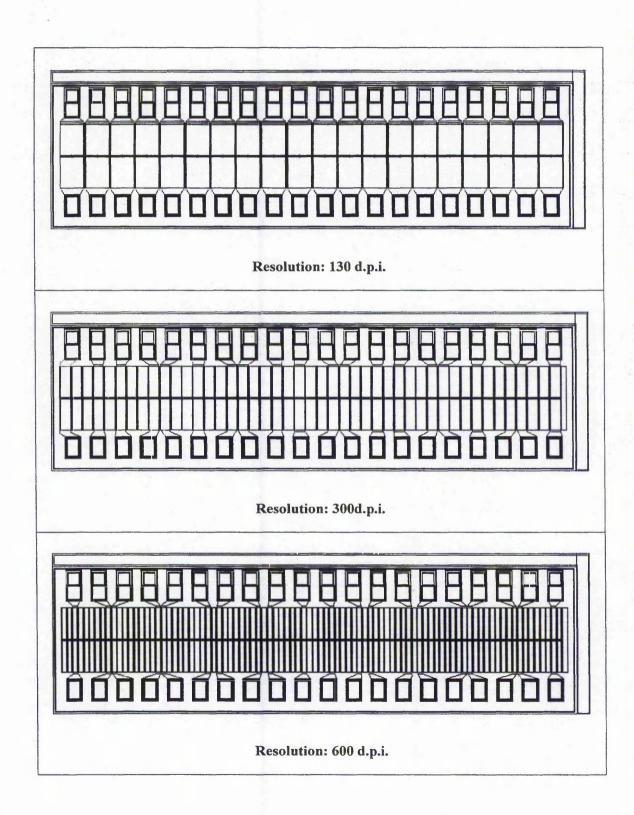

| Table 3-5  | Description of mmLETFEL printer test device structures, their dimensions<br>and graphical illustrations (for 130, 300 and 600dpi)                                                                                         |

| Table 3-6  | List of the test wafers fabricated and the types of characterisations<br>conducted (where S, Q, and T, correspond to sinusoidal, square, and<br>triangular, waveforms, respectively; and drive frequency is cited in kHz) |

| Table 3-7  | Calculated multiplying factor, K, used for correction of luminance values measured of mmLETFEL test devices                                                                                                               |

| Table 3-8  | Summary of circuit configuration used and related electrical expressions                                                                                                                                                  |

| Table 3-9  | Device parameters determined for insulator and base electrode materials                                                                                                                                                   |

| Table 3-10 | Luminance values of mmLETFEL TDEV11 grown with PolySi and TiW materials as base electrodes ( $Y_2O_3$ as insulators)                                                                                                      |

| Table 3-11 | Parameters calculated from Q-V characterisation of mmLETFEL TDEV11 grown with PolySi and TiW materials as base electrodes ( $Y_2O_3$ as insulators)                                                                       |

| Table 3-12 | Luminance values of a mmLETFEL test device grown with $Y_2O_3$ and $Si_3N_4$ materials as insulators (TiW as base electrodes)                                                                                             |

| Table 3-13 | Parameters calculated from Q-V characterisation of a mmLETFEL test device grown with $Y_2O_3$ and $Si_3N_4$ materials as insulators (TiW as base electrodes)                                                              |

| Table 4-1  | List of SPICE MOSFET model parameters for various commercial drivers                                                                                                                                                      |

| Table 4-2  | Corresponding description, units, and default values, for the SmartSpice n-<br>channel MOSFET Level=3 model parameters listed in Table 4-1                                                                                |

| Table 4-3  | List of SPICE model parameters, corresponding description, units, and default values for the Alcatel Mietec NDMOSHV model (for the principal transistor)                                                                  |

1 × 12

# List of Tables (Continued)

| Table 5-1  | Capacitance and resistance values calculated for both insulator and phosphor layers at various resolutions (where $d_i$ and $d_p$ are the fabricated thickness respectively) |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 5-2  | Experimental-simulated results of capacitance and diode breakdown voltage for TDEV11 of wafer CR123                                                                          |

| Table 5-3  | Simulated values of shunt capacitance, Csh, found for switching mmLETFEL devices at various resolutions                                                                      |

| Table 5-4  | mmLETFEL 'ON' and 'OFF' states during the switching operation                                                                                                                |

| Table 6-1  | Illustration of the various outcouplers and their corresponding coupling efficiencies                                                                                        |

| Table 6-2  | Proposed processing sequence incorporating new features for an vmLETFEL device                                                                                               |

| Table A1   | Mask Set 3: Small-area display devices                                                                                                                                       |

| Table A2   | Mask Set 3: Linear-array devices                                                                                                                                             |

| Table A3   | Mask Set 3: Test devices                                                                                                                                                     |

| Table A4   | Mask Set 2: Test devices                                                                                                                                                     |

| Table B1-1 | List of suggested parameters for dicing operation                                                                                                                            |

| Table B3-1 | List of suggested parameters for wire-bonding operation                                                                                                                      |

| Table C1   | SPICE model parameters of various commercial drivers                                                                                                                         |

| Table C2   | SmartSPICE MOSFET model level=3 parameters                                                                                                                                   |

| Table C3   | SPICE model parameters of Alcatel NDMOSHV model and SmartSPICE<br>MOSFET model level=2 parameters                                                                            |

盘

# List of Abbreviations

| A.C.     | Alternating Current                                           |

|----------|---------------------------------------------------------------|

| ACTFEL   | Alternating Current Thin-Film ElectroLuminescent              |

| AMEL     | Active Matrix ElectroLuminescent                              |

| APCVD    | Atmospheric Pressure Chemical Vapour Deposition               |

| arb      | Arbitrary                                                     |

| CAD      | Circuit Aided Design (or) Cathodic Arc Deposition             |

| CMF      | Central Microstructures Facilities                            |

| CMOS     | Complementary Metal-Oxide-Semiconductor                       |

| C-V      | Capacitance-Voltage                                           |

| CVD      | Chemical Vapour Deposition                                    |

| D.C.     | Direct Current                                                |

| DMOS     | Diffused Metal-Oxide-Semiconductor                            |

| eeLETFEL | edge-emitting Laterally-Emitting Thin-Film ElectroLuminescent |

| EL       | Electroluminescence                                           |

| GRIN     | Graded Refractive Index Number                                |

| HMD      | Head-Mounted Displays                                         |

| hvnMOS   | high-voltage n-channel Metal-Oxide-Semiconductor              |

| I.C.     | Integrated Circuit                                            |

| I-V      | Current-Voltage                                               |

| LED      | Light Emitting Diodes                                         |

| LETFEL   | Laterally-Emitting Thin-Film ElectroLuminescent               |

| LPCVD    | Low Pressure Chemical Vapour Deposition                       |

| L-V      | Luminance-Voltage                                             |

| MBE      | Molecular Beam Epitaxy                                        |

| mmLETFEL | micro-mirror Laterally-Emitting Thin-Film ElectroLuminescent  |

| MOCVD    | Metal Organic Chemical Vapour Deposition                      |

| MOSFET   | Metal-Oxide-Semiconductor Field Effect Transistor             |

| NMOS     | n-channel Metal-Oxide-Semiconductor                           |

| NMRC     | National Microstructures Research Centre                      |

| OEIC     | Opto-Electronic Integrated Circuit                            |

| PECVD    | Plasma Enhanced Chemical Vapour Deposition                    |

| PL       | Photoluminescence                                             |

100

# List of Abbreviations (Continued)

| PLZT     | Lead Lanthanum Zirconate Titanate                                            |

|----------|------------------------------------------------------------------------------|

| PMOS     | p-channel Metal-Oxide-Semiconductor                                          |

| Q        | Square waveform                                                              |

| Q-V      | Charge-Voltage                                                               |

| r.f      | Radio-Frequency                                                              |

| RAL      | Rutherford and Appleton Laboratories                                         |

| RIE      | Reactive Ion Etching                                                         |

| S        | Sinusoidal waveform                                                          |

| SEM      | Scanning Electron Microscopy                                                 |

| SLA      | SELFOC Lens Array                                                            |

| SOI      | Silicon-on-Insulator                                                         |

| SPICE    | Simulation Program with Integrated Circuit Emphasis                          |

| Т        | Triangular waveform                                                          |

| TAT      | Tri-layer Titanium/Tungsten-Aluminium-Titanium/Tungsten                      |

| TECAP    | Transistor Electrical Characterisation and Analysis Package                  |

| TFEL     | Thin-Film ElectroLuminescent                                                 |

| TNTU     | The Nottingham Trent University                                              |

| UV       | Ultra-Violet                                                                 |

| vmLETFEL | vertical micro-structures Laterally-Emitting Thin-Film<br>ElectroLuminescent |

| VWF      | Virtual Wafer Fabrication                                                    |

# List of Symbols

| Al                              | Aluminium                      |

|---------------------------------|--------------------------------|

| Ar                              | Argon                          |

| As <sub>2</sub> Se <sub>3</sub> | Amorphous Selenium             |

| a-Si:H                          | Hydrogenated Amorphous Silicon |

| Au                              | Gold                           |

| BaTiO <sub>3</sub>              | Barium Titanate                |

| BCl <sub>3</sub>                | Barium Chloride                |

| CCl <sub>3</sub>                | Calcium Chloride               |

| CF <sub>4</sub>                 | Carbon Tetrafluoride           |

| CHF <sub>3</sub>                | Freon 23                       |

| Cl <sub>2</sub>                 | Chlorine                       |

| $H_2$                           | Hydrogen                       |

| He                              | Helium                         |

| ITO                             | Indium Tin Oxide               |

| Mn                              | Manganese                      |

| $N_2$                           | Nitrogen                       |

| N <sub>2</sub> O                | Nitrous Oxide                  |

| Ne                              | Neon                           |

| NH <sub>3</sub>                 | Ammonia                        |

| O <sub>2</sub>                  | Oxygen                         |

| PolySi                          | polysilicon                    |

| Se                              | Selenium                       |

| Si                              | Silicon                        |

| Si <sub>3</sub> N <sub>4</sub>  | Silicon Nitride                |

| SiCl <sub>4</sub>               | Silicon Tetrachloride          |

| SiH <sub>4</sub>                | Silane                         |

| SiO <sub>2</sub>                | Silicon Dioxide                |

| SION                            | Silicon Oxynitride             |

| TiW                             | Titanium/Tungsten              |

| T <sub>ox</sub>                 | Thermal Oxide                  |

| $Y_2O_3$                        | Yttrium Oxide                  |

|                                 |                                |

# List of Symbols (Continued)

| Zn     | Zinc                          |

|--------|-------------------------------|

| ZnS    | Zinc Sulphide                 |

| ZnS:Mn | Manganese doped Zinc Sulphide |

| ZnSe   | Zinc Selenide                 |

# List of Units

| Ω      | Ohms                      |

|--------|---------------------------|

| °C     | Celsius                   |

| °F     | Fahrenheit                |

| А      | Ampere                    |

| Å      | Angstrom                  |

| a.u.   | Arbitrary Unit            |

| С      | Coulomb                   |

| Cd     | Candela                   |

| d.p.i. | Dots Per Inch             |

| eV     | Electron Volts            |

| F      | Farads                    |

| fL     | Foot-Lamberts             |

| Hz     | Hertz                     |

| J      | Joules                    |

| 1      | Litres                    |

| lm     | Lumens                    |

| p.p.i. | Pixels Per Inch           |

| p.p.m. | prints/pages per minute   |

| sccm   | Standard Cubic Centimetre |

| V      | Volts                     |

| W      | Watts                     |

# List of Constants & Variables

| ρ                              | Resistivity of a given material                                    |

|--------------------------------|--------------------------------------------------------------------|

| ρ(x)                           | Resistivity as a function of distance x into a given material      |

| ε <sub>0</sub>                 | Permittivity of Vacuum at 8.854x10 <sup>-12</sup> Fm <sup>-1</sup> |

| $\eta_{eff}$                   | Luminous Efficiency                                                |

| ε <sub>i</sub>                 | Dielectric Constant of an Insulator                                |

| ε <sub>p</sub>                 | Dielectric Constant of a Phosphor                                  |

| ΔQ                             | Transferred Charge Density                                         |

| ε <sub>r</sub>                 | Relative Permittivity of a given material                          |

| $\Delta w_a$                   | Average Width of Emitting Aperture                                 |

| Δx                             | Average Width of Aperture                                          |

| А                              | Area                                                               |

| Ac                             | Area of Focusing Circle of luminance metre                         |

| A <sub>dpi</sub>               | Active Area of a given material at a given resolution in d.p.i.    |

| A <sub>emit</sub>              | Area of mmLETFEL test device Emitting Aperture                     |

| $\mathrm{BV}_{\mathrm{diode}}$ | Breakdown Voltage of the zener diodes                              |

| С                              | Capacitance                                                        |

| $C[v_L(t)]$                    | Dynamic Capacitance across the mmLETFEL test device                |

| C <sub>dpi</sub>               | Capacitance of a given material at a given resolution in d.p.i.    |

| $C_i$                          | Insulator Capacitance                                              |

| C <sub>off</sub>               | Total Capacitance before device turn-on                            |

| Con                            | Total Capacitance after device turn-on                             |

| C <sub>p</sub>                 | Phosphor Capacitance                                               |

| Cs                             | Sense Capacitor                                                    |

| d                              | Thickness of a given layer                                         |

| D                              | Zener Diodes of a mmLETFEL equivalent circuit                      |

| di                             | Thickness of an Insulator                                          |

| $d_p$                          | Thickness of a Phosphor                                            |

| Ei                             | Electric Field of an Insulator                                     |

| $\mathbf{E_{in}}$              | Input Energy Density                                               |

| E <sub>p</sub>                 | Electric Field of a Phosphor                                       |

| f                              | Drive Frequency                                                    |

xxii

# List of Constants & Variables (Continued)

| G                           | Gain or sensitivity of photoreceptor in percentage                   |

|-----------------------------|----------------------------------------------------------------------|

| hı                          | Height of Microlens                                                  |

| h <sub>pl</sub>             | Height of Planarisation layer                                        |

| i(t)                        | Instantaneous Current                                                |

| I <sub>ds</sub>             | Drain-Source Current of a transistor                                 |

| К                           | Factor of Luminance                                                  |

| 1                           | Length of a mmLETFEL device                                          |

| L                           | Luminance at any given voltage                                       |

| $L_{diff}$                  | Luminance range between 'ON' and 'OFF' states                        |

| $L_{corrected}$             | Corrected Luminance                                                  |

| $L_{measured}$              | Measured Luminance                                                   |

| L <sub>Vm</sub>             | Luminance at a Modulated Voltage of $V_m$                            |

| P <sub>in</sub>             | Power Dissipation / Power Consumption / Input Power Density          |

| Q                           | Charge                                                               |

| q(t)                        | Instantaneous Charge                                                 |

| Q'                          | Charge Density remaining after drive voltage goes to zero            |

| Q <sub>pk</sub>             | Charge Density at the Peak Voltage of $V_{pk}$                       |

| Q <sub>th</sub>             | Charge Density at the Threshold Voltage of $V_{th}$                  |

| Q <sub>to</sub>             | Charge Density at the Turn-on Voltage of $V_{to}$                    |

| R <sub>c</sub>              | Sense Resistor                                                       |

| $\mathbf{R}_{\mathrm{dpi}}$ | Resistance of a given material at a given resolution in d.p.i.       |

| R <sub>e</sub>              | Resistance of top electrode of a mmLETFEL device                     |

| R <sub>i</sub>              | Insulator Resistance                                                 |

| R <sub>m</sub>              | Resistance of base electrode of a mmLETFEL device                    |

| R <sub>p</sub>              | Phosphor Resistance                                                  |

| R <sub>s</sub>              | Series Resistor                                                      |

| $R_{sh}$                    | Sheet Resistance of a given material                                 |

| R <sub>z</sub>              | Resistance associated with hot-electron emission at interface states |

| S                           | Drum speed in p.p.m.                                                 |

| ts                          | Travelling speed of photosensitive material under test               |

| V <sub>0</sub>              | Initial potential of photosensitive material after charging          |

| <b>v</b> <sub>1</sub> (t)   | Drive Voltage                                                        |

# List of Constants & Variables (Continued)

| v <sub>2</sub> (t)         | Voltage at node of contact to mmLETFEL Top Electrode          |

|----------------------------|---------------------------------------------------------------|

| v <sub>3</sub> (t)         | Voltage at node of contact to mmLETFEL Base Electrode         |

| V <sub>d</sub>             | Discharged voltage of photosensitive material                 |

| $V_{\text{diff}}$          | Switching voltage range for a hvnMOS device                   |

| $V_{ds}$                   | Drain-Source Voltage of a transistor                          |

| V <sub>exc</sub>           | Excitation/Drive Voltage                                      |

| $V_{exc(pk-pk)}$           | Peak-to-peak excitation/drive voltage                         |

| $V_{gs}$                   | Gate-Source Voltage of a transistor                           |

| v <sub>L</sub> (t)         | Voltage Drop across mmLETFEL Test Device                      |

| $V_{\text{letfel}}$        | Voltage across a mmLETFEL device                              |

| V <sub>letfel(pk-pk)</sub> | Peak-to-peak voltage across a mmLETFEL device                 |

| V <sub>m</sub>             | Modulated Voltage                                             |

| V <sub>p</sub>             | Voltage Drop across the Phosphor Layer                        |

| $V_{pk}$                   | Peak Voltage                                                  |

| Vr                         | Residual voltage on photosensitive material after discharging |

| V <sub>th</sub>            | Threshold Voltage                                             |

| V <sub>th(pk-pk)</sub>     | Peak-to-peak threshold voltage                                |

| $V_{th,ph}$                | Threshold Voltage for the Phosphor Layer                      |

| V <sub>to</sub>            | Turn-on Voltage                                               |

| W                          | Width of mmLETFEL test device                                 |

| w                          | Width of a mmLETFEL device                                    |

| Wa                         | Width of Emitting Aperture                                    |

| W <sub>bp</sub>            | Width of Black Polyamide                                      |

| Wd                         | Drain Width of a transistor                                   |

| Wg                         | Pitch of Waveguides                                           |

| w <sub>1</sub>             | Base diameter of Microlens                                    |

| w <sub>mc</sub> .          | Width of micro-mirror metallised coating                      |

| W <sub>mm</sub>            | Width of micro-mirror                                         |

| Ws                         | Width of Sidewalls                                            |

|                            |                                                               |

# **Contents**

# 1 Introduction

| 1.1 | Revie | w of Electrophotographic Printing                             | . 3  |

|-----|-------|---------------------------------------------------------------|------|

|     | 1.1.1 | Background                                                    | 3    |

|     | 1.1.2 | Electrophotographic Printing Process                          | 5    |

|     | 1.1.3 | Photoreceptors                                                | 7    |

|     | 1.1.4 | Light Sources                                                 | 8    |

| 1.2 | Revie | w of Alternating Current Thin-Film Electroluminescent Devices | 10   |

|     | 1.2.1 | Introduction                                                  | 10   |

|     | 1.2.2 | Previous Work on ACTFEL devices as image bar arrays           | . 13 |

|     | 1.2.3 | Current Work on Active Matrix Electroluminescent Displays     | . 14 |

| 1.3 | Revie | w of Laterally-Emitting Thin-Film Electroluminescent Devices  | 15   |

|     | 1.3.1 | Introduction                                                  | . 15 |

|     | 1.3.2 | Previous Work on mmLETFEL linear-array devices                | . 18 |

| 1.4 | Over  | Overview                                                      |      |

|     | 1.4.1 | Objectives of the Investigation                               | . 19 |

|     | 1.4.2 | Preliminary Investigations                                    | . 23 |

|     | 1.4.3 | Summary of the Thesis                                         | .27  |

|     |       |                                                               |      |

1**-**i

# **1** INTRODUCTION

Alternating Current Thin-Film ElectroLuminescent (ACTFEL) devices – consisting of a phosphor layer sandwiched between two insulating layers and from which light is produced upon application of an electric field across the structure – had been demonstrated to emit light laterally, at an order of magnitude greater than the conventional surface emission, due to the inherent wave-guiding property in these devices.<sup>1</sup>

As a result of this observation, edge-emitting TFEL devices had been proposed as an alternative low-cost optical image bar array in electrophotographic printing.<sup>2, 3, 4</sup> However, these edge-emitting devices required the formation of an emitting facet on a glass substrate, which can be problematic. Therefore, a more elegant and potentially more reliable technique would be to redirect this laterally emitted light from the substrate via reflecting microstructures, termed as Laterally-Emitting TFEL (LETFEL) devices.<sup>5, 6, 7, 8, 9</sup>

The outcoupling of this useful lateral emission using the micro-mirror Laterally-Emitting Thin-Film ElectroLuminescent (mmLETFEL) technology not only increases the overall luminance of the device, but with a significant reduction in the active area required to produce the same intensity, can lead to the achievement of higher resolution devices.<sup>10, 11</sup>

Thus, there is the potential of developing this mmLETFEL technology into high-intensity high-resolution linear bar arrays,<sup>12</sup> as the use of Silicon (Si) substrates and standard Si fabrication processes yields the potential for integration of driver electronics within the same device. This eliminates the need for external electronic drive circuits, minimising the cost of manufacture and assembly, as well as the complexity of external yield-damaging wire-bonds. Furthermore, continuous research has produced more efficient mmLETFEL devices, <sup>13, 14, 15, 16</sup> thereby providing the possibility of mmLETFEL devices being developed into high-intensity integrated light source as an alternative image bar array in electrophotographic printing.

Hence, the main objective of this research is to assess the feasibility and commercial viability of developing the current mmLETFEL technology into an integrated mmLETFEL device termed as the Opto-Electronic Integrated Circuit (OEIC) – consisting of a mmLETFEL pixel defined in the same device with its corresponding drive electronics.

The investigation into developing this OEIC for optical image bar applications, i.e. electrophotographic printing, is analysed and assessed by fabrication, characterisation and modelling of mmLETFEL test devices on Si wafers with pre-fabricated base electrodes, characterisation and modelling of commercially available drivers. Finally demonstration has been made of the overall working principle via theoretical simulation of the OEIC equivalent circuit.

The following sub-sections are introduced to give a brief review and understanding of the background surrounding the investigation to be undertaken, i.e. the electrophotographic printing process, ACTFEL and LETFEL technologies, and mmLETFEL printhead prototype development. The chapter concludes with an outline of the objectives of the research to be carried out and an overview of the contents of the remaining chapters in the thesis.

### 1.1 REVIEW OF ELECTROPHOTOGRAPHIC PRINTING

### 1.1.1 Background

In the 1930's, the only available copying method was the photostat process based on silver halide photography, where reproduction could take days and the availability of the service was limited.<sup>17</sup> The need for a simple and inexpensive device that would allow any type of document to be copied led to the invention of electrophotography by Chester Carlson in 1937.<sup>18</sup> His review<sup>19</sup> in the history of charged powder development from Selenyi<sup>20</sup> to as far back as Lichtenberg,<sup>21</sup> gave him the idea of forming electrostatic latent images using photoconductivity to selectively discharge a surface-charged insulator; and of developing this latent image by dusting with powders charged electrostatically.

During the 1950's and 1960's, major companies such as Xerox, Eastman Kodak, IBM and RCA, recognised the potential of Carlson's discovery and were primarily interested in copying. However, IBM was soon interested in developing faster computer printers and was then licensed by Xerox for research and development in electrophotography targeted at printer applications. IBM concentrated research on organic photoreceptors, mono-component development systems and a means of electro-optically forming the latent image on the photoconductive surface.

In 1973, Xerox introduced the first modern electrophotographic printer, the model 1200. By 1975, and 1976, IBM and Canon introduced the first laser-based electrophotographic computer printer, the model IBM 3800 with a speed of 215 pages per min (ppm), and the model Canon LBP2000 C1 operating at 31 ppm,<sup>22</sup> with both using HeNe gas lasers to address the photoconductive drum. By then, it was thought that the electrophotography technology had matured, and research had ceased.

However, in the late 1970's, interest in further research in electrophotography was fueled by the development of other alternative technologies to challenge the laser electrophotography, such as ionography (research and manufacture by Delphax Systems),<sup>23</sup> and magnetography (work by Bull Peripheriques),<sup>24</sup> hence renewing the attention and significantly heightening the commercial value of electrophotographic technology.

Further, a fourth printing technology, bubblejet (produced by Canon and Hewlett-Packard in the early 1980's),<sup>25</sup> introduced the use of semiconductor lasers in place of gas lasers, which can be packaged in transistor-size containers and can be modulated by current-control.

By the mid-1980's, the laser-spinning polygon system was found to be able to be replaced with an all-solid-state device. An array of liquid crystal shutters was used to address the photoreceptor, with a uniform light source behind the shutters and a SELFOC Graded Refractive Index Number (GRIN)<sup>26</sup> lens in the front for the imaging.

The first products using this light shutter technology were manufactured by Epson and Casio, but only up to 7 ppm and 9 ppm respectively.<sup>27, 28, 29</sup> Then, Oki Electric and NEC introduced printers utilising light-emitting diode (LED) arrays, with a print speed of 10 ppm and 8 ppm respectively.<sup>30, 31</sup> IBM and Eastman Kodak too, introduced their new LED printers at 12 ppm, and 92 ppm respectively.<sup>32, 33</sup> In order to compete with the laser-polygon systems, these "image bar" technologies had to maintain a sufficient light uniformity and the interconnection of light elements to driver electronics at an affordable cost.

### 1.1.2 Electrophotographic Printing Process

Electrophotography is defined as those processes involved that utilise the interaction of light and electricity as basic elements for image formation.<sup>34</sup> Xerography describes those processes involved in the creation of electrostatic charge patterns on surfaces of photoconducting insulators.

The electrostatic image is formed by first charging and then exposing a photoconductive insulating surface to a light pattern. The image is developed, transferred to paper, and then fused onto it. The photoconductive insulator can be used many times to produce thousands of prints. **Figure 1-1** shows a typical configuration of an electrophotographic printer in its cross-sectional view.

There are six distinctive steps to the process, and a brief description is given in the following, where the numbers correspond to the ones in bold brackets in **Figure 1-1**.

1. Charge

A corona discharge caused by air breakdown uniformly charges the cleaned surface of the rotating photoconductive drum.

2. Expose

Light discharges the insulating photoconductive drum, producing a latent image. At selected positions along the drum (at any one time), regions are either exposed or not. Photons absorbed by the photoconductive drum generate electron-hole pairs, and when these free carriers are swept to the respective anode or cathode, charge recombination occurs. Selective reduction of surface charge across the drum builds up the electrostatic latent image.

3. Develop

In regions where the Coulombic force is sufficient, the electrostatically charged toner particle is attracted to the photoconductive surface, i.e. the electrostatic latent image, thus transforming it into a real image.

4. Transfer

The back of the paper is first corona charged with a charge opposite to that of the toner particles. Another Coulombic force pulls the paper against the toned photoconductor surface, thus allowing transfer of the toner from the drum to paper.

5. Fuse

The transferred toner, which is electrostatically held on the paper, is fused onto the paper permanently by heating the back surface in a heated roller system. The toner becomes soft and flows into the matrix of the paper. The perceived blackness of the image is due to the decreased reflectance of the paper caused by the toner.

6. Clean

Before the drum is reused, any excess toner left on the photoconductive drum is cleaned out by discharging and physically cleaning it using a cleaning blade.

As a result, an electronically stored image is printed onto normal untreated paper.

### 1.1.3 Photoreceptors

There are 2 types of photoreceptors: inorganic photoreceptors and organic photoreceptors.