FOR REFERENCE ONLY

\_7 JAN 2003

10346680

ProQuest Number: 10183101

All rights reserved

INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

ProQuest 10183101

Published by ProQuest LLC (2017). Copyright of the Dissertation is held by the Author.

All rights reserved.

This work is protected against unauthorized copying under Title 17, United States Code Microform Edition © ProQuest LLC.

ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 – 1346

#### PERFORMANCE STUDIES OF THIN FILM ELECTROLUMINESCENT (TFEL) DEVICES

Muragesan Sethu

A thesis submitted in partial fulfilment of the requirements of The Nottingham Trent University for the degree of Doctor of Philosophy

> Electrical and Electronic Engineering Division The Nottingham Trent University Nottingham, U.K.

> > September 2002

#### Abstract

The study of mechanisms that contribute to the characteristics of Alternating Current Thin Film Electroluminescent (ACTFEL) display devices are presented. Primarily the investigation is based on Y<sub>2</sub>O<sub>3</sub> thin film insulator, ZnS:Mn thin film phosphor and ACTFEL devices, which were fabricated by radio frequency magnetron sputtering with the effects of deposition parameters, post deposition annealing temperature, and source material. An extensive study was performed of the thin film  $Y_2O_3$  grown on silicon (100) substrate for its role as a high dielectric constant insulator material. The reproducibility problem associated with this thin film material was addressed whereby the lifetime of the sputtering target was identified to be a contributing factor. The crystallite structural growth of the oxide is empirically compared with its charge properties. In general, the interface state density between the sputtered  $Y_2O_3$  and Silicon has a high value, extending to 10<sup>13</sup> cm<sup>-2</sup> eV<sup>-1</sup> in some discrete state, however the density was significantly reduced by thermal treatment in vacuum. Thin film ZnS:Mn deposited at 200 °C substrate temperature has the best crystallinity both on Silicon and on  $Y_2O_3$  thin film and hence has the best phosphor efficiency. Additionally, annealing the thin film also improved the phosphor efficiency, unlocking the true potential of the phosphor, which was mainly due to an increase in number of radiative sites. The interfacial charge density and distribution at the interface of the insulator/phosphor is shown to be critical in determining the operation characteristics of the ACTFEL device whereby annealing and ageing affects it. Devices annealed at 400°C had the most stable ageing behaviour. SiON insulator ACTFEL device exhibited a large positive shift in LV characteristics, which was primarily due to a decrease in SiON layer capacitance. Both  $Y_2O_3$  and SiON insulators ACTFEL device have advantages and disadvantages associated with their use.

#### Preface

The need for an interface between the human visual system and machine information database has ensured that optoelectronic displays have a key role in our everyday life. These optoelectronic devices rely heavily on the discipline of optics and solid state physics, which are the fundamental expectation for work on this subject. The interpretation of what is meant by optoelectronic covers the interaction of light with matter in gaseous, liquid or solid form and the devices, which depend on these interactions.

The Cathode ray tube has proved to be an outstandingly efficient light-emitting device with excellent colour capability for use in information displays. However the current push for flat panel displays is quite intense, and much confusion exists as to where development and commercialisation will occur most rapidly. The success of a technology is governed by its survival through the three gateways, which are Market, Management and Technology.

From a technological viewpoint, Thin Film Electroluminescent (TFEL) devices have many advantages such as lightweight, wide viewing angle, solid-state, bright, and high-contrast emission. All these aspects are very amenable for manufacturing a practical flat panel information display.

The purpose of this work is to give an understanding of the technology. Most of the important operation physics are dealt with. This understanding is indispensable for better perception of the failure mechanism and is necessary for a correct measurement of parameters. The stress here is on its underlying assumption and limitations and how one would employ the presented methods to derive the device characteristics of interest.

M. Sethu

#### Acknowledgements

This thesis would not have been possible without the contribution of many individuals, to whom I would like to extend my thanks,

Firstly, my supervisor and mentor, Professor Clive B. Thomas for providing me the opportunity to undertake this study, his support and encouragement and his challenging methods, which exceptionally contributed toward my personal development as a researcher.

Dr. Wayne M. Cranton, my second supervisor for his contribution, understanding and kindness, which ensured continuous progress of the research programme.

Dr. Costas Tsakonas for his timely help which considerably improved my understanding of semiconductor physics and MIS theory. In this respect, I would also like to thank Dr. Jörg Rüdiger my friend, for his professional support in my work.

Sincere thanks also goes to Dr. Robert Ranson for all his help, especially for the organisation of the fabrication laboratory. The other members of the Optoelectronic research group, A. Liew, D. Koutsogeorgis, T. Nam and my ex-colleagues, Dr. E. Mastio, Dr. M. Craven and Dr. P. Theng for their contribution to the on going success of the team. The technicians of the Electrical & Electronic Division and Judith Kipling from Mechanical Division for all their help during my time at the university.

Prof. J. Silver from Greenwich University for performing the Raman measurements on my samples. Dr. E.K. Evangelou from Ioannina University, Greece for giving me the opportunity to visit that university and broadening my horizon in high- $\kappa$  thin film materials. Prof. H.S. Reehal from South Bank University for allowing me to use the Ellipsometer for refractive index measurement. EPSRC for loaning me the thermal imaging system. Dr. R. Stevens from Rutherford Appleton Laboratory for providing the SiON samples and his collaborative participation with the research group. Lite Array Inc., USA for providing the commercial ACTFEL panels and some of the financial support, which kept me motivated.

All my teachers that have been a part of my life, without them I would not have been able to undertake further studies.

My dearest friends both here in the UK and elsewhere for their invaluable support during those challenging periods of my life. The Hindu Youth Group, UK, which actively kept me fit, both mentally and physically.

Finally, I am eternally grateful to my beloved family members for their love, which I have to admit was the most important of all. My brother and sisters for providing me the provisions, which I couldn't have done without. Dr. M.V. Moorthy and Dr. Pushpam Moorthy for their loving attention on my well being during my time in the UK. A heartfelt thanks to Surina, for her continued love, patients and encouragement. My mother to whom I dedicate this thesis for everything she has done for me.

### **List of Publications**

Electrical and Crystallinity Study of Yttrium Oxide Thin Film for use in ACTFEL device, M. Sethu, *PREP 2001, University of Keele, U.K.*

Materials Processing and Device Engineering for Laterally Emitting Thin Film Electroluminescent Miniature Displays, W.M. Cranton, C.B. Thomas, D. Koutsogeorgis, E. Mastio, M. Craven, R. Stevens, R. Ranson, M. Sethu, J. Rudiger, S. Barros, A. Liew, C.Tsakonas and P.Theng, *Microdisplays 2001, Society of Information Displays Digest of Paper, Pg.* 102

Miniature Transverse TFEL Displays, W.M. Cranton, C.B. Thomas, D.C. Koutsogeorgis, R.M. Ranson, S.C. Liew, C. Tsakonas, M.Sethu, *IDMC* 1-20.4 2002, *Korea*

Electrical and Structural Characteristics of r.f. magnetron deposited Y<sub>2</sub>O<sub>3</sub> films on nsilicon, E.K. Evangelou, M. Sethu, C.B. Thomas, S. Cocco, D.T. Dekadjevi, M. Fanciulli, G. Seguini & S. Spiga, *Si-Workshop 2002, Genova, Italy*

Electrical Characterisation of Behaviour and Ageing Mechanism of Alternating Current Thin Film Electroluminescent Device, M. Sethu, C.B. Thomas, C.M. Cranton & R.M. Ranson, *The 7th Asian Symposium on Information Display, 2002, Singapore*

### **Statement of Original Work**

The work presented in this thesis represents the author's contribution to the ongoing research at the Nottingham Trent University. The research programme is to understand the physics and engineering of Thin Film Electroluminescent display devices and to investigate all the mechanisms contributing to device performance. Experimental approach has been demonstrated to achieve this goal.

The author was responsible for the deposition and characterisation of all the thin film materials employed in this programme. The author also designed and commissioned all the characterisation systems as presented in this work, including all the software programmes utilised for the measurements and automation.

### **Table of Contents**

| Abstract                      | ü     |

|-------------------------------|-------|

| Preface                       | iii   |

| Acknowledgement               | iv    |

| List of Publications          | vi    |

| Statement of Original Work    | vii   |

| Table of Contents             | viii  |

| List of Equations             | xiv   |

| List of Figures               | xvi   |

| List of Tables                | xxii  |

| List of Abbreviations         | xxiii |

| List of Symbols and Variables | xxv   |

### Chapter 1

### Introduction

| 1.1 | Elect | columinescence                                     | 1-1  |

|-----|-------|----------------------------------------------------|------|

| 1.2 | Alter | nating Current Thin Film Electroluminescent Device | 1-3  |

| 1.3 | Revie | ew of EL Performance Mechanisms                    |      |

| 1.3 | .1    | Material Properties                                | 1-6  |

| 1.3 | .2    | Effects of Electric Field                          | 1-10 |

| 1.3 | .3    | Environmental Effects                              | 1-12 |

| 1.4 | Aim                | 1-13          |

|-----|--------------------|---------------|

| 1.5 | Objectives         | 1-13          |

| 1.6 | Overview of Thesis | 1 <b>-</b> 14 |

| 1.7 | References         | 1-15          |

### Chapter 2

### **Experimental Engineering**

| 2.1 Hy  | pothesis of the Experiments           | 2-1  |

|---------|---------------------------------------|------|

| 2.2 Fat | prication of the ACTFEL device        |      |

| 2.2.1   | Thin Film Deposition                  | 2-2  |

| 2.2.2   | Metalisation and Patterning           | 2-5  |

| 2.3 Ele | ctrical Characterisation              |      |

| 2.3.1   | High Voltage Amplifier                | 2-6  |

| 2.3.2   | ACTFEL Current and Charge Measurement | 2-6  |

| 2.3.3   | Capacitance and Current Measurement   | 2-8  |

| 2.4 Lui | minance and Imagery Characterisation  |      |

| 2.4.1   | Computerised Probe Station            | 2-11 |

| 2.4.2   | Edge Emission Luminance Measurement   | 2-13 |

| 2.4.3   | Photoluminescence Measurement         | 2-16 |

| 2.4.4   | Thermal Imaging                       | 2-18 |

| 2-19 |

|------|

|      |

| 2-20 |

| 2-20 |

| 2-22 |

|      |

#### 2.7 References

### Chapter 3

### Properties of Y<sub>2</sub>O<sub>3</sub> Thin Film

| 3.1 | Introduction                         | 3 <b>-</b> 1 |

|-----|--------------------------------------|--------------|

| 3.2 | Growth Parameters                    | 3-2          |

| 3.3 | Structural and Dielectric Properties | 3-5          |

| 3.4 | Oxygen Annealing                     | 3-12         |

| 3.5 | Electrical Stressing                 | 3-12         |

| 3.6 | Breakdown Strength                   | 3-13         |

| 3.7 | Summary and Conclusions              | 3-14         |

| 3.8 | References                           | 3-16         |

#### Chapter 4

### Capacitance Analysis of Y<sub>2</sub>O<sub>3</sub> MIS Diode

| 4.1 | Introduction                      | 4-1  |

|-----|-----------------------------------|------|

| 4.2 | General MIS CV Measurement Theory | 4-2  |

| 4.3 | Flatband Voltage Determination    | 4-6  |

| 4.4 | Charges in a Non-Ideal MIS System | 4-7  |

| 4.5 | Yttrium Oxide MIS Diode           | 4-11 |

| 4.6 | Summary and Conclusions           | 4-28 |

| 4.7 | References                        | 4-30 |

#### Chapter 5

#### **Properties of ZnS:Mn Phosphor**

| Intro | duction                                              | 5-1                                                                                               |

|-------|------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| Struc | tural Properties                                     | 5-2                                                                                               |

| Photo | oluminescence                                        | 5-9                                                                                               |

| Elect | rical Properties                                     |                                                                                                   |

| .1    | Dielectric Constant                                  | 5-14                                                                                              |

| .2    | Electrical Stressing                                 | 5-15                                                                                              |

| .3    | Breakdown and Leakage Current                        | 5-17                                                                                              |

| Sum   | mary and Conclusions                                 | 5-21                                                                                              |

| Refe  | rences                                               | 5-24                                                                                              |

|       | Struc<br>Photo<br>Electr<br>4.1<br>4.2<br>4.3<br>Sum | Photoluminescence<br>Electrical Properties<br>4.1 Dielectric Constant<br>4.2 Electrical Stressing |

xi

#### Chapter 6

#### **Characteristics of ACTFEL Device**

| 6.1 | Intro   | duction                                       | 6-1  |

|-----|---------|-----------------------------------------------|------|

| 6.2 | Expe    | riment Results and Discussions                |      |

| 6.2 | .1      | The Need for Annealing                        | 6-2  |

| 6.2 | .2      | Effect of Annealing on Device Characteristics | 6-4  |

| 6.2 | .3      | Electro-Optical Ageing Behaviour              |      |

| 6   | .2.3.1  | Vacuum Environment                            | 6-12 |

| e   | 5.2.3.2 | Ambient Environment                           | 6-21 |

| 6.2 | .4      | Comparison with SiON Insulator ACTFEL Device  | 6-23 |

| 6.2 | 5       | Device Electrode Breakdown                    | 6-30 |

| 6.3 | Sum     | mary and Conclusions                          | 6-32 |

| 6.4 | Refe    | rences                                        | 6-35 |

|     |         |                                               |      |

#### <u>Chapter 7</u>

#### **Thesis Conclusions**

| 7.1 | Introduction                                             | 7-1  |

|-----|----------------------------------------------------------|------|

| 7.2 | Conclusions of the Studies                               | 7-2  |

| 7.3 | Further Work                                             |      |

| 7.3 | .1 Proposed Engineering for Optimising ACTFEL Device     | 7-6  |

| 7.3 | .2 Insulator Materials                                   | 7-9  |

| 7.3 | .3 ZnS:Mn Thin Film Study                                | 7-9  |

| 7.3 | .4 Attenuation Coefficient                               | 7-10 |

| 7.3 | .5 Y <sub>2</sub> O <sub>3</sub> Target Surface Analysis | 7-12 |

| 7.5 | References                                               | 7-13 |

### Appendix A

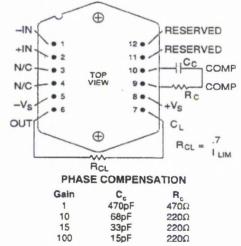

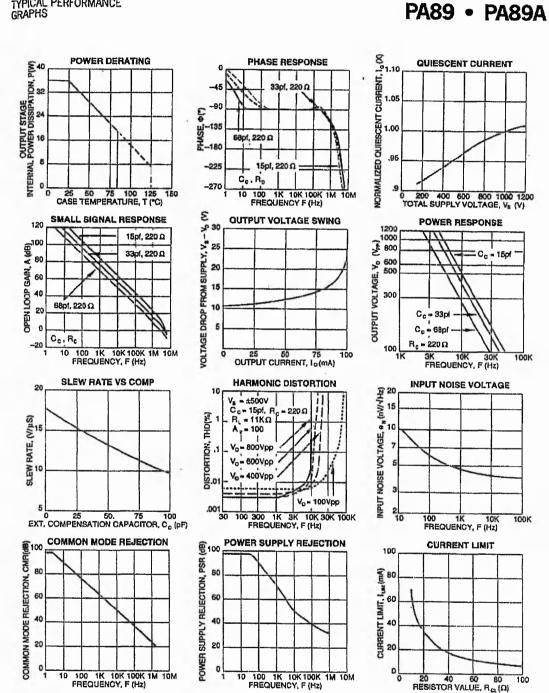

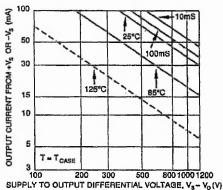

| High Voltage Amplifier Design Details      | A-1          |

|--------------------------------------------|--------------|

| Data Sheet of PA89 Operational Amplifier   | A-3          |

| Appendix B                                 |              |

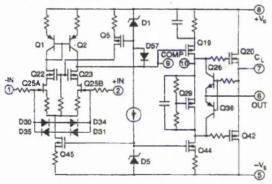

| Pictures of Other Characterisation Systems | B-1          |

| Appendix C                                 |              |

| Constants of Pure Yttrium Oxide Crystal    | C-1          |

| Appendix D                                 |              |

| Pictures of Broken-down ACTFEL devices     | D <b>-</b> 1 |

| Appendix E                                 |              |

| Labview Programs                           | E-1          |

# **List of Equations**

| Eq. 1.1  | Relationship between light emission and power                                       |

|----------|-------------------------------------------------------------------------------------|

| Eq. 2.1  | Equation to calculate thin film thickness                                           |

| Eq. 2.2  | Equation to calculate instantaneous charge in ACTFEL device                         |

| Eq. 2.3  | Equation to calculate instantaneous current in ACTFEL device                        |

| Eq. 2.4  | Equation to calculate thin film capacitance                                         |

| Eq. 2.5  | Equation to calculate thin film breakdown field                                     |

| Eq. 2.6  | Equation to calculate charge storage capacity of thin film                          |

| Eq. 2.7  | Snell's Law                                                                         |

| Eq. 2.8  | Equation to calculate photon energy                                                 |

| Eq. 2.9  | Bragg equation to calculate crystal plane spacing                                   |

| Eq. 2.10 | Relationship between plane spacing and lattice constant for cubic crystal structure |

| Eq. 2.11 | Equation to calculate crystallite size                                              |

| Eq. 3.1  | Molecular dipole moment                                                             |

| Eq. 3.2  | Definition for dielectric constant                                                  |

| Eq. 4.1  | Capacitance of MIS diode                                                            |

| Eq. 4.2  | Gate voltage drop across components in a MIS system                                 |

| Eq. 4.3  | Equation to calculate flatband voltage of MIS system                                |

| Eq. 4.4  | Equation to calculate charge distribution in an insulator layer                     |

| Eq. 4.5  | Equation to calculate transferred charge                                            |

| Eq. 4.6  | Equation to calculate flatband voltage with distributed oxide trapped charge        |

| Eq. 4.7  | Equation to calculate flatband voltage with oxide trapped charge                    |

| Eq. 4.8  | Equation to calculate maximum depletion width                                       |

| Eq. 4.9  | Equation to calculate inversion capacitance with maximum depletion width            |

|          |                                                                                     |

# List of Equations

| Eq. 4.10 | Equation to calculate interface trapped charge for certain band bending                         |

|----------|-------------------------------------------------------------------------------------------------|

| Eq. 4.11 | Silicon surface capacitance at flatband condition                                               |

| Eq. 4.12 | Silicon surface capacitance in strong accumulation                                              |

| Eq. 4.13 | Silicon surface capacitance in depletion and week inversion region                              |

| Eq. 4.14 | Debye length                                                                                    |

| Eq. 4.15 | Equation to calculate interface trap density at a certain band bending                          |

| Eq. 4.16 | Equation to calculate interface trap density during pinning at large interface state            |

|          |                                                                                                 |

| Eq. 6.1  | Equation to calculate the peak phosphor field in an ACTFEL device                               |

| Eq. 6.2  | Ratio of voltage drop across the phosphor layer                                                 |

| Eq. 6.3  | Relationship between total ACTFEL capacitance and the insulator and phosphor layer capacitances |

| Eq. 6.4  | Equation to calculate the pre-clamping interface state charge                                   |

| Eq. 6.5  | Relationship external measured current and ACTFEL mechanism current                             |

| Eq. 6.6  | Equation to calculate tunneling current                                                         |

| Eq. 7.1  | Luminance in an optical guide as a function of material length                                  |

| Figure 1.1  | Schematic of a typical Alternating Current Thin Film Electroluminescent device                           |

|-------------|----------------------------------------------------------------------------------------------------------|

| Figure 1.2  | Energy-band diagram of the double-insulating-layer-type ACTFEL device                                    |

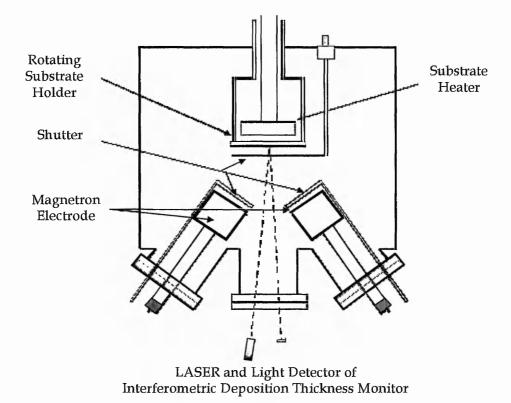

| Figure 2.1  | Schematic layout of the chamber configuration utilised for the depositions of the thin film materials    |

| Figure 2.2  | Picture of the main R.F. sputtering chamber utilised to deposited the $Y_2O_3$ and the ZnS:Mn thin films |

| Figure 2.3  | Picture of the substrate heater                                                                          |

| Figure 2.4  | Stainless Steel contact mask for circular diodes                                                         |

| Figure 2.5  | Stainless Steel contact mask edge-emitters device                                                        |

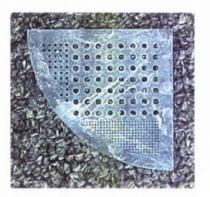

| Figure 2.6  | Block diagram of the Current/Charge measurement unit                                                     |

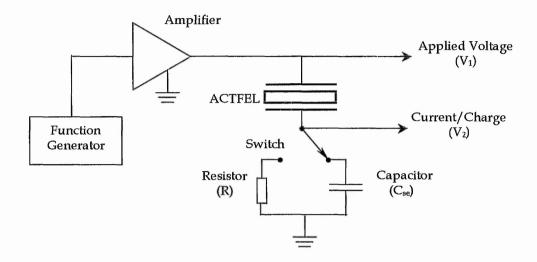

| Figure 2.7  | Pictures of the Capacitance-Bridge and Current meter probe stations                                      |

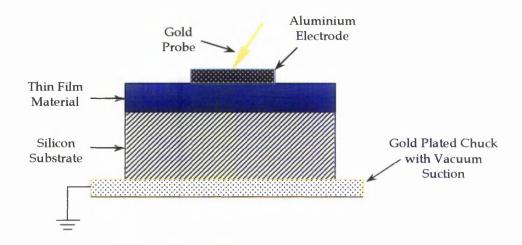

| Figure 2.8  | Cross section of Metal Insulator Semiconductor diode                                                     |

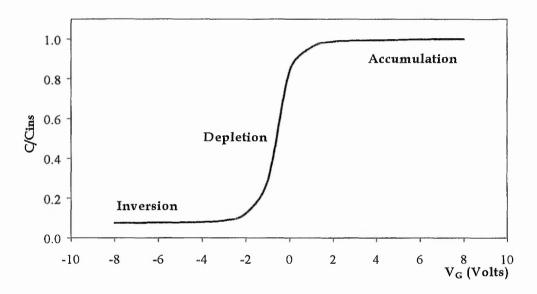

| Figure 2.9  | Typical normalised plot of Capacitance versus Voltage characteristics MIS diode of n-type silicon        |

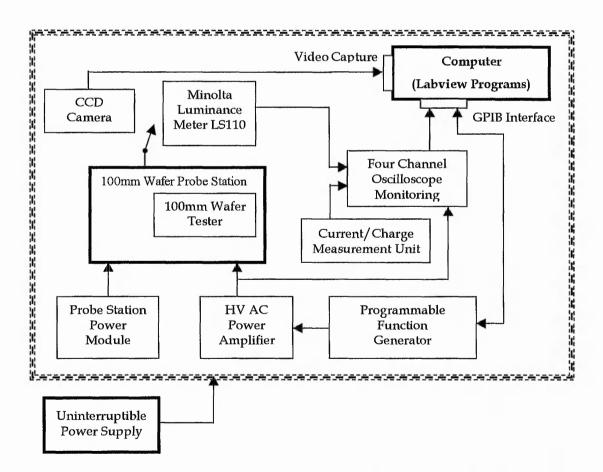

| Figure 2.10 | Schematic diagram of the computerised wafer Probe Station                                                |

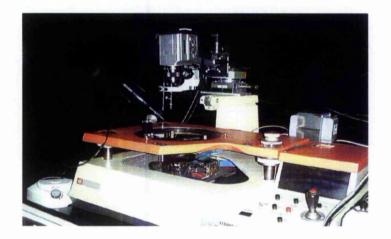

| Figure 2.11 | Picture of computerised 1034X wafer Probe Station                                                        |

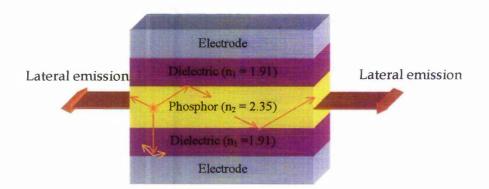

| Figure 2.12 | Schematic cross section of ACTFEL device structure showing lateral emission                              |

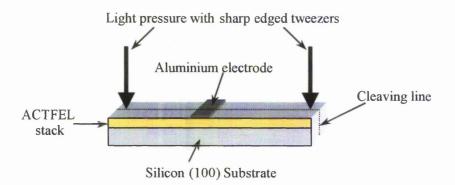

| Figure 2.13 | Diagram showing the process of cleaving a TFEL device in preparation for an edge-out device              |

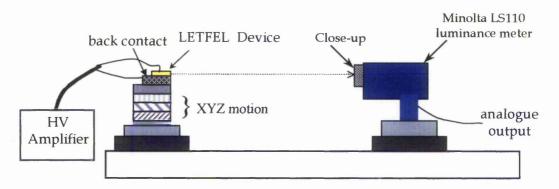

| Figure 2.14 | Schematic diagram of the LETFEL Edge-out luminance measurement system                                    |

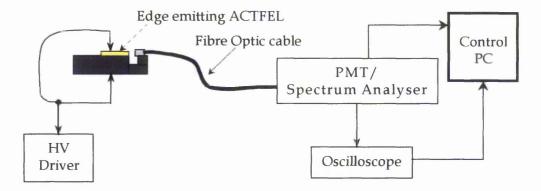

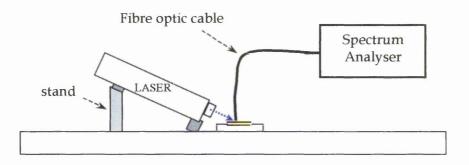

| Figure 2.15 | Transient/Spectrum Analyser measurement configuration for LETFEL device                                  |

| Figure 2.16 | Picture of edge-emission fibre optic luminance detection block                                           |

| Figure 2.17 | Schematic arrangement for Photoluminescent measurement                                                   |

| Figure 2.18 | Picture of an optical 10nm band-pass filter used for transient<br>Photoluminescent measurement           |

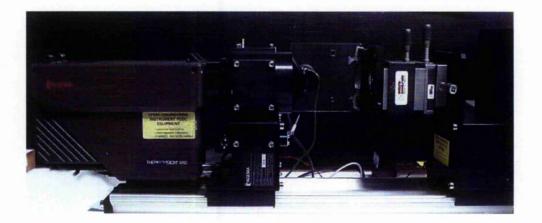

| Figure 2.19 | Picture of the Infrared thermal imaging system                                                           |

| Figure 2.20 | Picture of the vacuum chamber for luminance degradation measurement                                      |

|             |                                                                                                          |

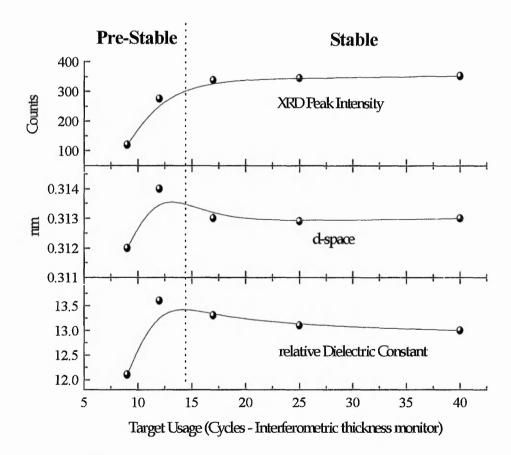

| Figure 3.1  | XRD structural analysis and dielectric constant of thin film $Y_2O_3$ as a function of target usage lifetime                            |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

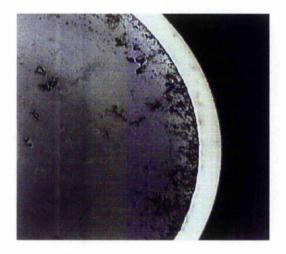

| Figure 3.2  | Picture of a used 7.5 cm Y <sub>2</sub> O <sub>3</sub> target                                                                           |  |

| Figure 3.3  | XRD pattern of peak (222) for $Y_2O_3$ thin films                                                                                       |  |

| Figure 3.4  | XRD structural analysis and dielectric constant for thin film $Y_2O_3$ as a function of sample annealed temperature                     |  |

| Figure 3.5  | Raman Spectrum for $Y_2O_3$ thin films grown on Silicon (100) substrate                                                                 |  |

| Figure 3.6  | Current-Voltage curves for $Y_2O_3$ samples                                                                                             |  |

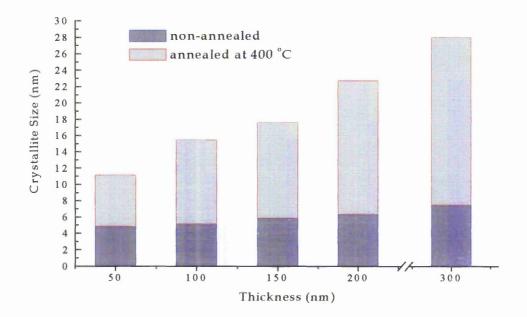

| Figure 3.7  | Plot of crystallite size with increase in $Y_2O_3$ thin film thickness                                                                  |  |

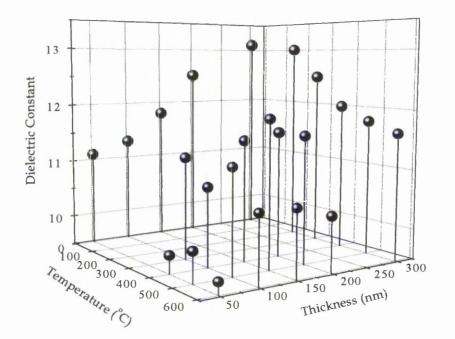

| Figure 3.8  | Summary of the average measured dielectric constant for thin film $Y_2O_3$ as a function of sample thickness and annealed temperature   |  |

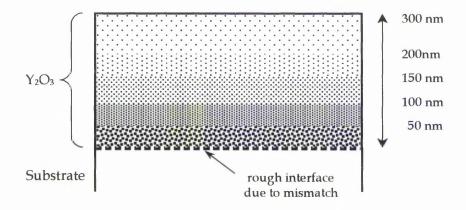

| Figure 3.9  | Pictorial crystalline defect thickness model of sputtered $Y_2O_3$ thin film on Silicon (100) substrate                                 |  |

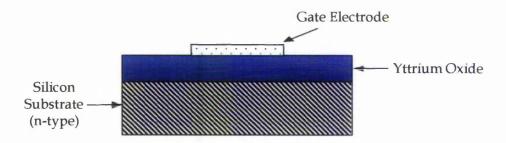

| Figure 4.1  | Cross section of Y2O3 MIS diode                                                                                                         |  |

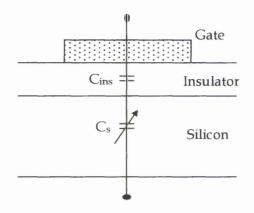

| Figure 4.2  | Schematic of a simple equivalent circuit of MIS diode                                                                                   |  |

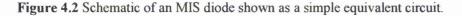

| Figure 4.3  | Potential band diagram of a MIS structure with an n-type semiconductor at flatband                                                      |  |

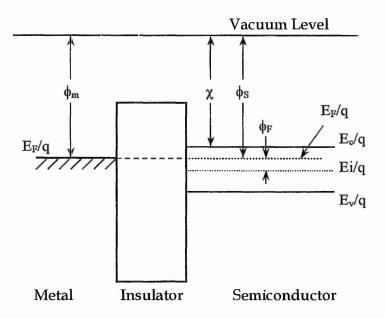

| Figure 4.4  | Illustration of the operation of a MIS system, showing the band bending at accumulation, depletion and inversion of the silicon surface |  |

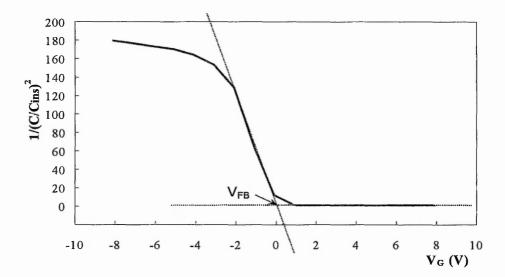

| Figure 4.5  | Diagram illustrating the method used to calculated flatband voltage                                                                     |  |

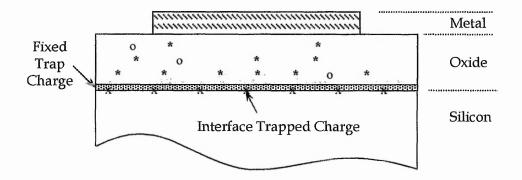

| Figure 4.6  | Illustration of a MIS structure with charges and their possible locations                                                               |  |

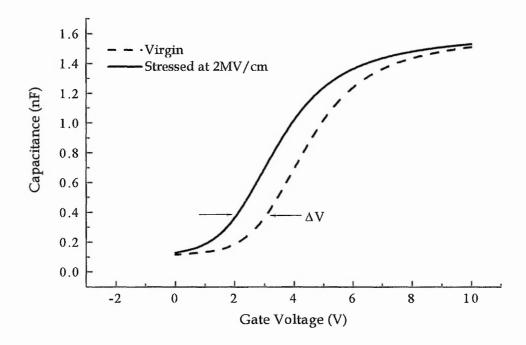

| Figure 4.7  | CV curves of $Y_2O_3$ MIS diode before and after stressing at positive                                                                  |  |

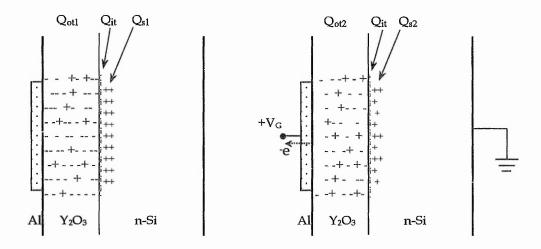

| Figure 4.8  | Cross-section of $Y_2O_3$ MIS structure showing oxide trapped, interface trapped and silicon surface charges                            |  |

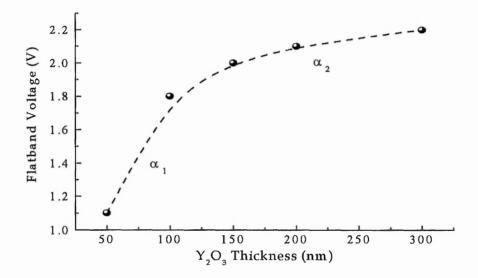

| Figure 4.9  | Flatband Voltage for non-annealed samples as a function of $Y_2 O_3$ thickness                                                          |  |

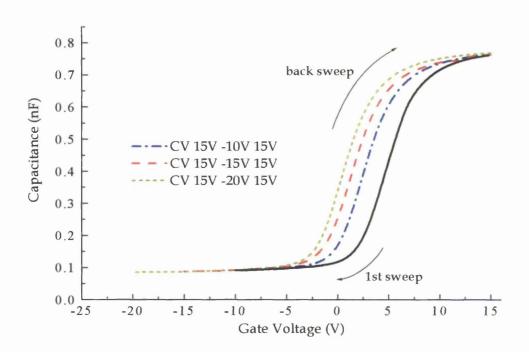

| Figure 4.10 | CV curves of non-annealed $Y_2 O_3$ MIS sample with different negative span voltage                                                     |  |

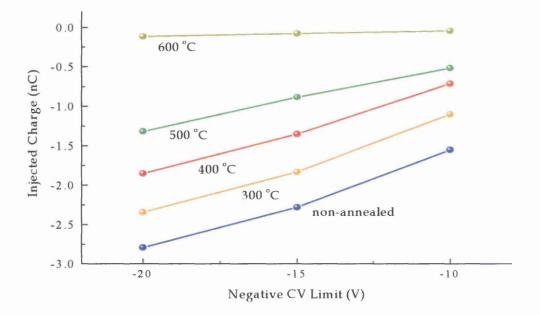

| Figure 4.11 | Plot of the amount of charge injected as a function of maximum negative voltage bias of a CV measurement for $Y_2O_3$ MIS diode         |  |

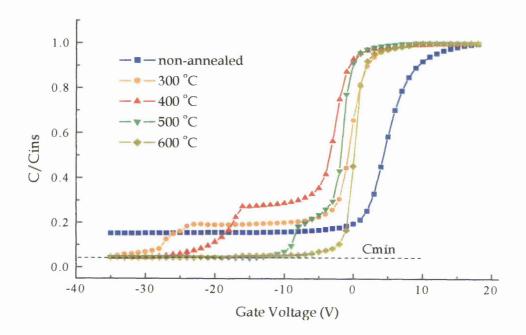

| Figure 4.12 | CV curves for $Y_2O_3$ MIS diodes annealed at various temperatures                                                                      |  |

|             |                                                                                                                                         |  |

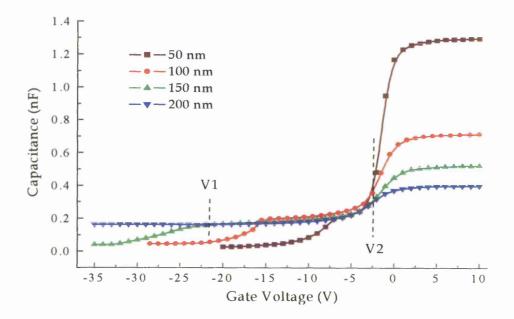

| Figure 4.13 | CV curves of samples with different thickness annealed at 400 °C.                                                                                       |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

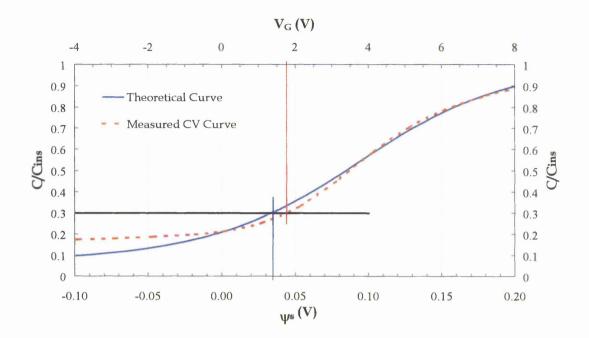

| Figure 4.14 | Plots of a theoretical high frequency capacitance versus silicon surface band bending graph compared with a measured CV curve, of a $Y_2O_3$ MIS sample |

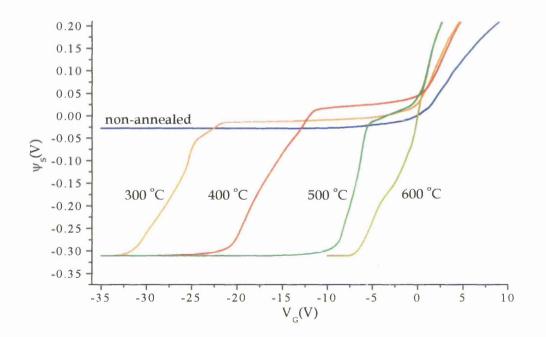

| Figure 4.15 | Plot of silicon surface band bending versus gate voltage for Y2O3 MIS samples annealed at different temperatures                                        |

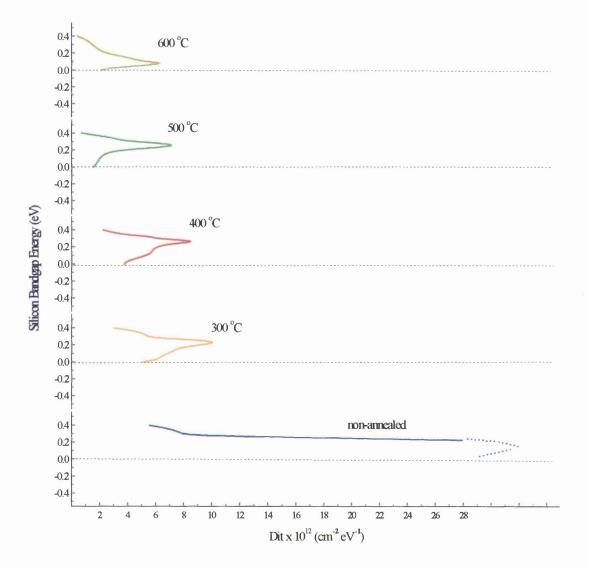

| Figure 4.16 | The calculated density of interface states versus silicon bandgap for $Y_2O_3$ MIS diodes, annealed at different temperatures                           |

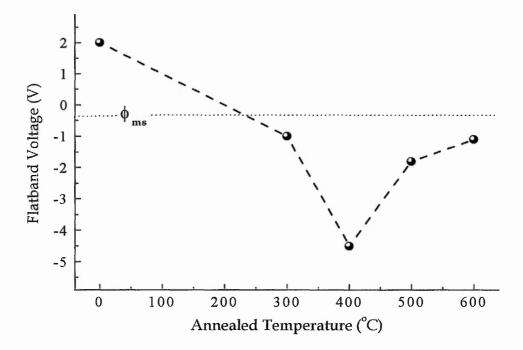

| Figure 4.17 | The measured flatband voltage for $Y_2O_3$ MIS samples as a function of annealed temperature                                                            |

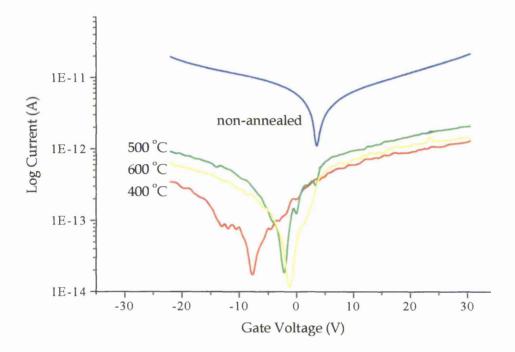

| Figure 4.18 | IV curves for $Y_2O_3$ MIS diodes annealed at different temperatures                                                                                    |

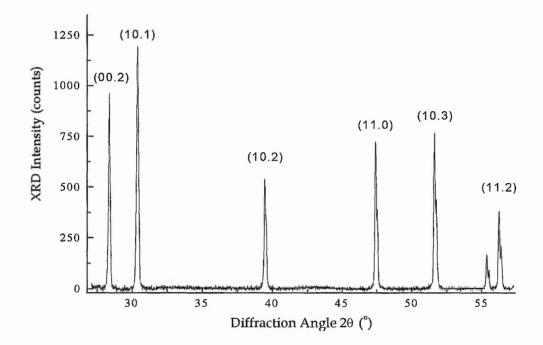

| Figure 5.1  | XRD pattern of ZnS:Mn powder source material used in sputtering target                                                                                  |

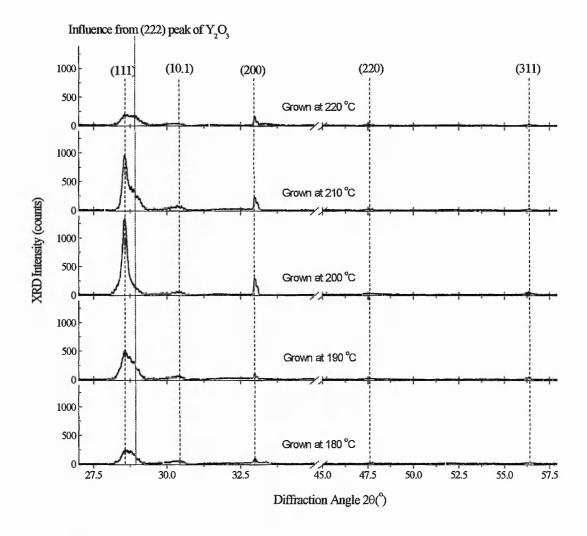

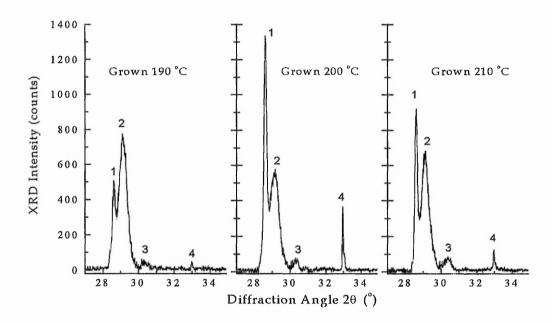

| Figure 5.2  | XRD patterns of non-annealed thin film ZnS:Mn grown at different substrate temperature fabricated on $Y_2O_3$ thin film                                 |

| Figure 5.3  | XRD patterns of thin film ZnS:Mn grown at different substrate temperatures on Y2O3 thin film, grown at 200 °C and annealed at 500 °C                    |

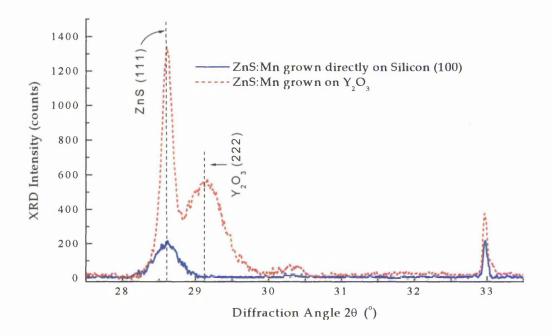

| Figure 5.4  | XRD patterns of thin film ZnS:Mn grown on $Y_2O_3$ thin film and on Silicon (100) substrate                                                             |

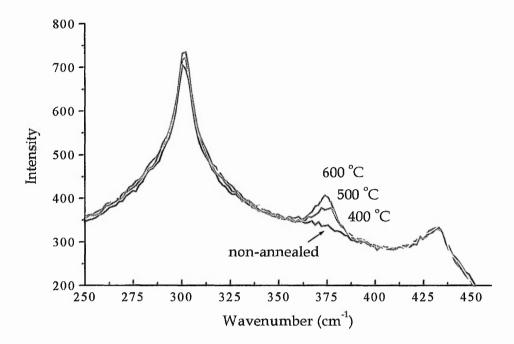

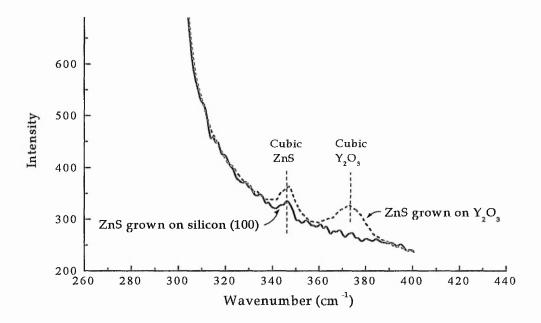

| Figure 5.5  | Raman Spectrum for ZnS:Mn thin film grown on $Y_2O_3$ thin film and on Silicon (100) substrate                                                          |

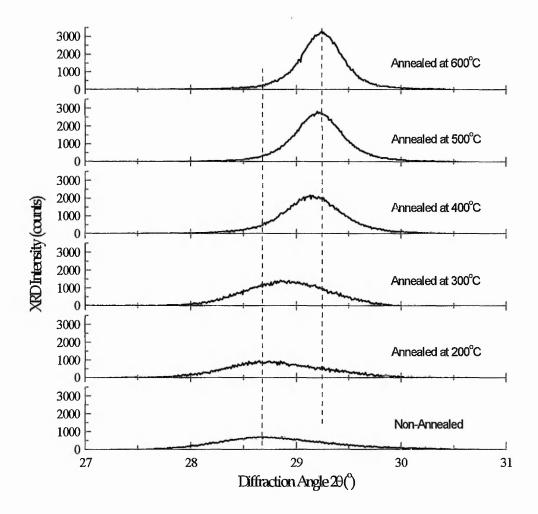

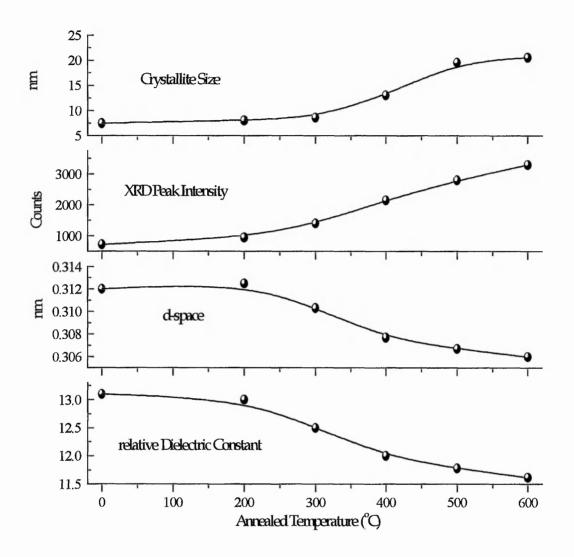

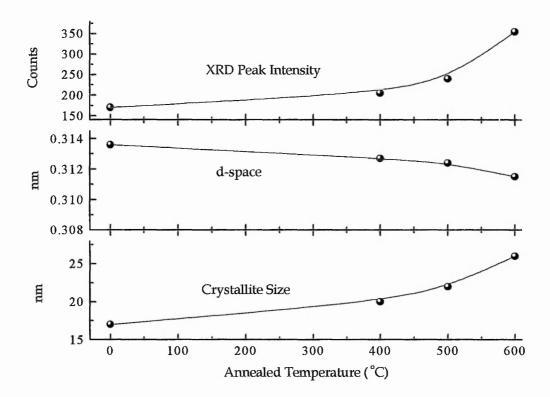

| Figure 5.6  | XRD structural analysis for thin film ZnS:Mn grown on silicon (100) at 200 °C as a function of sample annealed temperature                              |

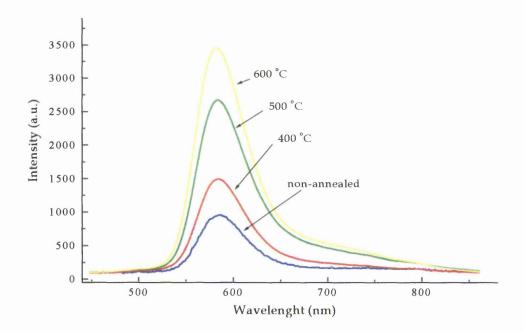

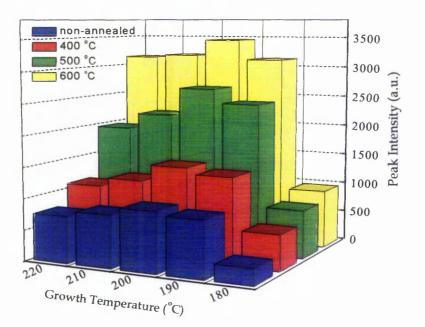

| Figure 5.7  | PL spectra for ZnS:Mn thin film annealed at various temperatures                                                                                        |

| Figure 5.8  | Summary of the peak PL intensity for ZnS:Mn thin film grown on silicon substrate as a function of sample fabricated and annealed temperature            |

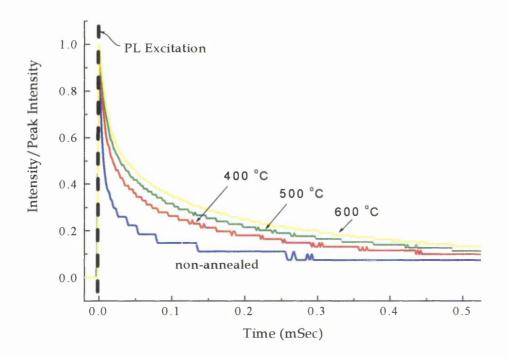

| Figure 5.9  | Transient emission decay of PL from ZnS:Mn thin film grown on silicon<br>at 200 °C and annealed at various temperatures                                 |

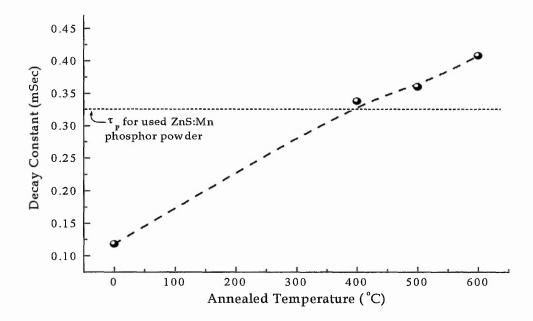

| Figure 5.10 | Transient PL decay constant for ZnS:Mn thin film as a function of sample anneal temperature                                                             |

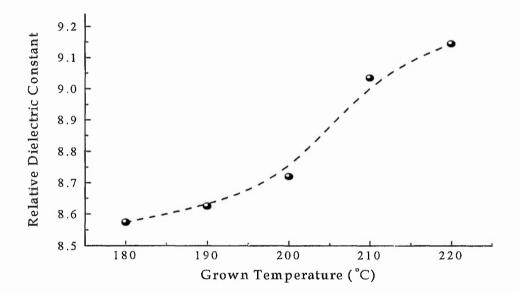

| Figure 5.11 | Dielectric constant of non-annealed ZnS:Mn thin film grown on Silicon substrate as a function of sample grown temperature                               |

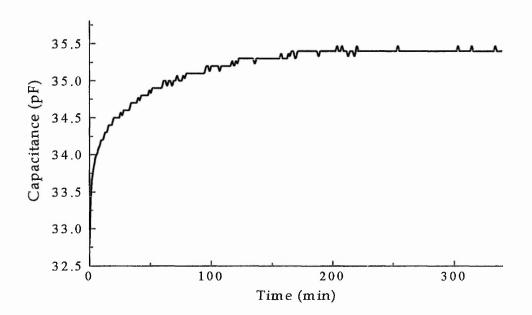

| Figure 5.12 | Plot of capacitance for ZnS:Mn thin film as a function of stressing time at 0.5 MV/cm electric field across the diode                                   |

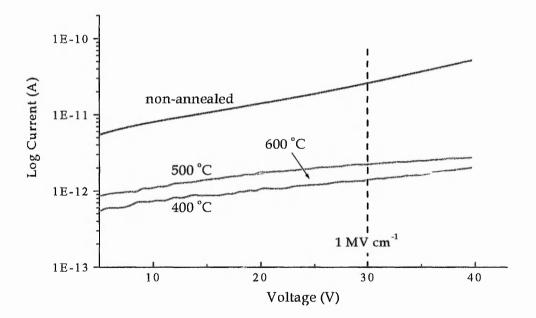

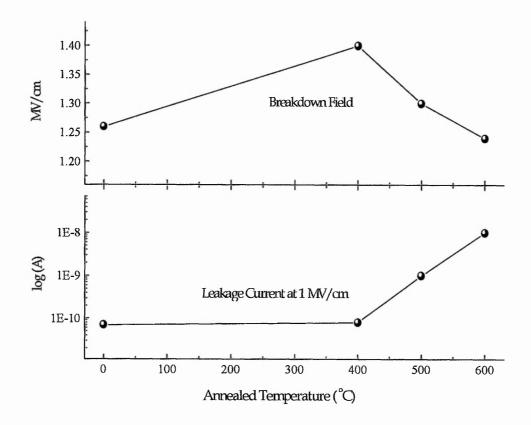

| Figure 5.13 | Characteristics of breakdown field strength and leakage current for thin film ZnS:Mn diodes as a function of anneal temperature                                                                             |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

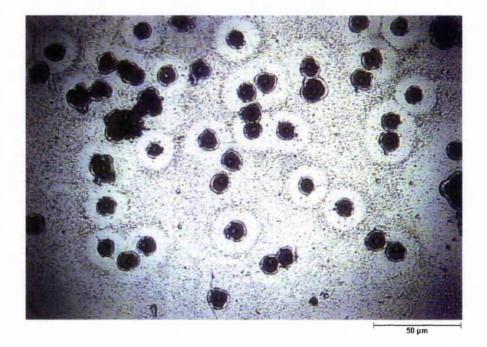

| Figure 5.14 | Picture of spots on ZnS:Mn thin film on silicon, broken down diode                                                                                                                                          |  |

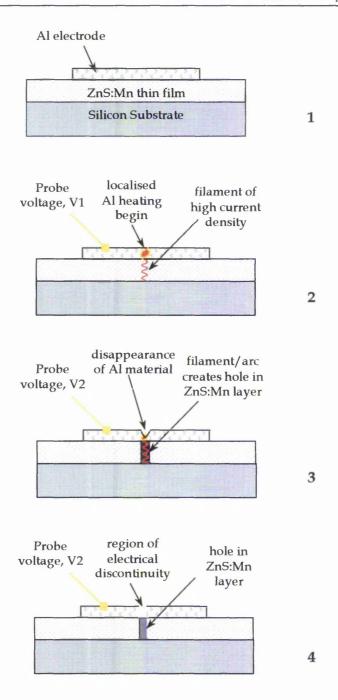

| Figure 5.15 | Illustration of the processes which creates LDB in ZnS:Mn thin film                                                                                                                                         |  |

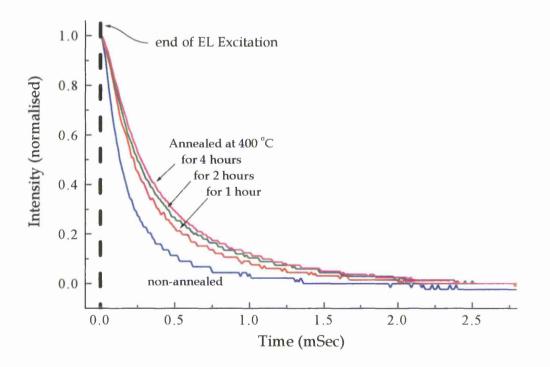

| Figure 6.1  | Transient emission decay of EL from ACTFEL device for a non-annealed sample and samples annealed at 400 °C for various times                                                                                |  |

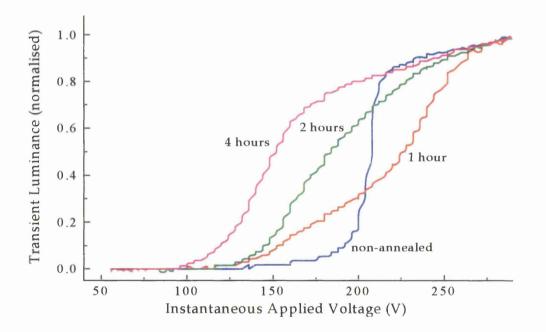

| Figure 6.2  | Transient EL as a function of the instantaneous applied voltage from a non-annealed sample and samples annealed at 400 °C for various times                                                                 |  |

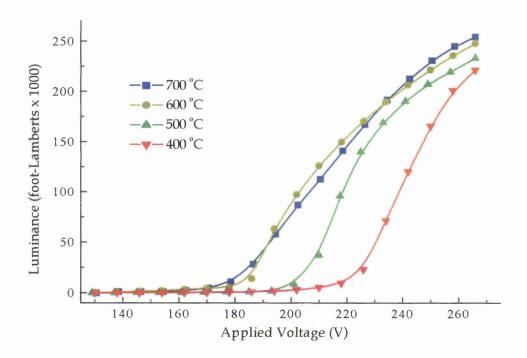

| Figure 6.3  | LV characteristics for ACTFEL edge-emission samples annealed at different temperatures                                                                                                                      |  |

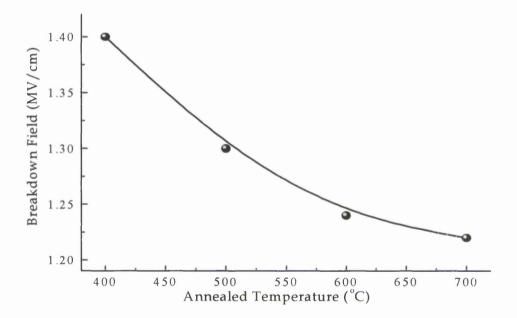

| Figure 6.4  | Measured breakdown field for ZnS:Mn thin film MIS diode as a function of sample annealed temperature                                                                                                        |  |

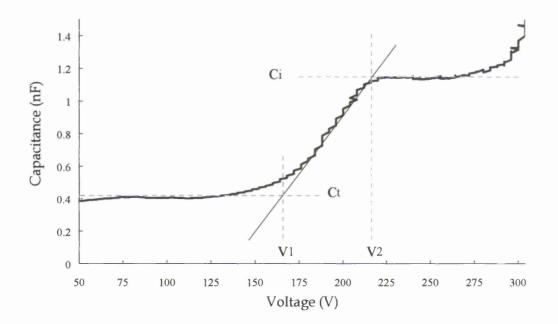

| Figure 6.5  | CV curves for an ACTFEL device                                                                                                                                                                              |  |

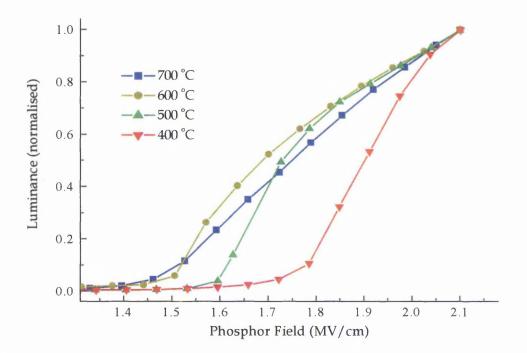

| Figure 6.6  | Luminance versus phosphor field for ACTFEL devices annealed at different temperatures                                                                                                                       |  |

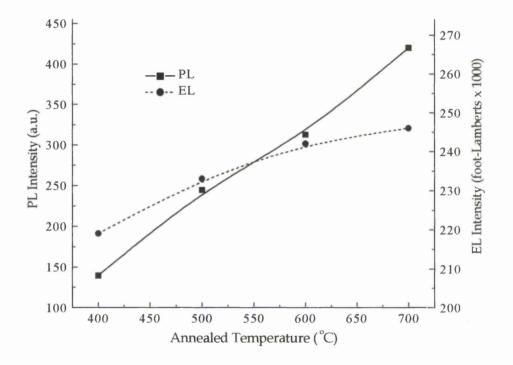

| Figure 6.7  | Summary of the peak intensity of ZnS:Mn thin film and EL luminance of ACTFEL device as a function of annealing temperature                                                                                  |  |

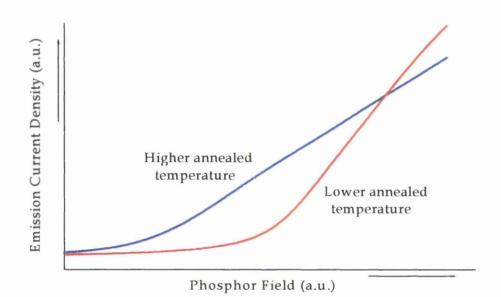

| Figure 6.8  | Model of the possible emission current density profile from the ZnS:Mn/Y <sub>2</sub> O <sub>3</sub> interface as a function of phosphor field for ACTFEL samples annealed at lower and higher temperatures |  |

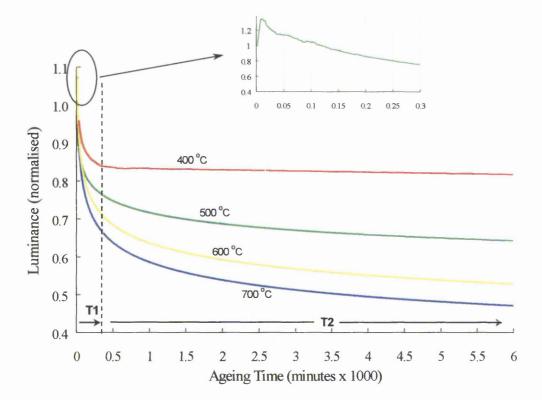

| Figure 6.9  | Luminance as a function of operation time in for ACTFEL devices<br>annealed at different temperatures                                                                                                       |  |

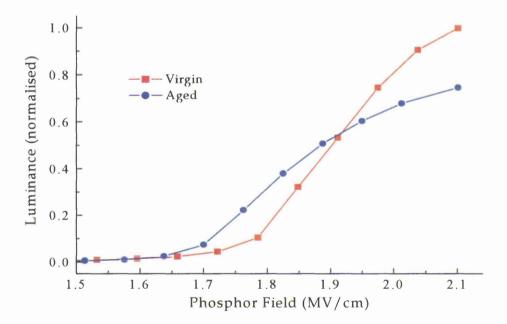

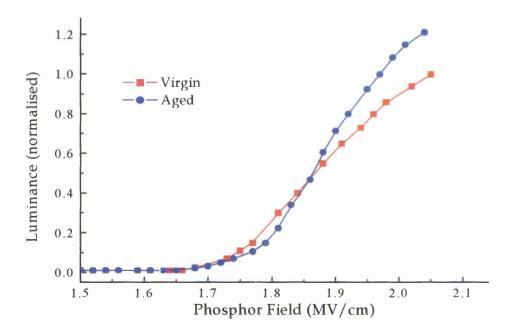

| Figure 6.10 | Luminance as a function of phosphor field of an ACTFEL device annealed at 400 °C in its virgin and aged state.                                                                                              |  |

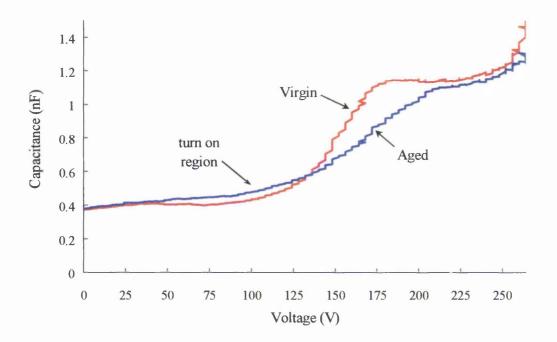

| Figure 6.11 | CV curves for an ACTFEL device during its virgin state and after ageing                                                                                                                                     |  |

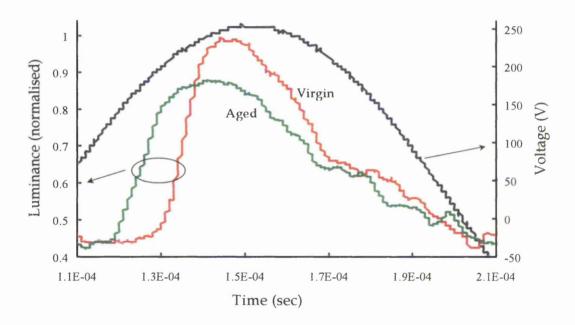

| Figure 6.12 | Transient EL luminance response to applied device voltage for an ACTFEL device during its virgin state and after ageing                                                                                     |  |

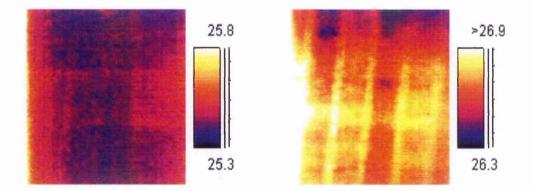

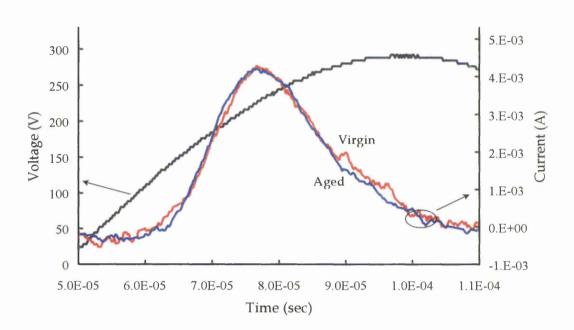

| Figure 6.13 | Thermal images of an ACTFEL device surface in it off and fully on conditions                                                                                                                                |  |

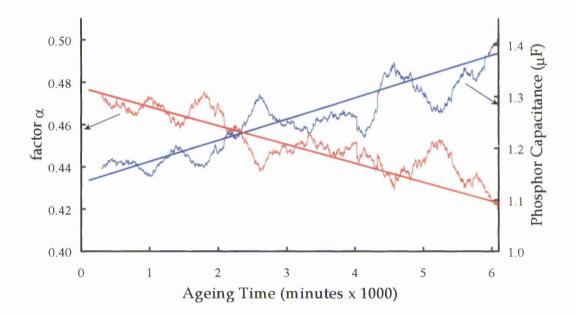

| Figure 6.14 | Plot of the increase in phosphor capacitance and reduction in factor $\boldsymbol{\alpha}$                                                                                                                  |  |

| Figure 6.15 | Tunneling currents response to applied voltage for an ACTFEL device annealed at 400 °C in its virgin and aged for 200 hours in vacuum                                                                       |  |

|             |                                                                                                                                                                                                             |  |

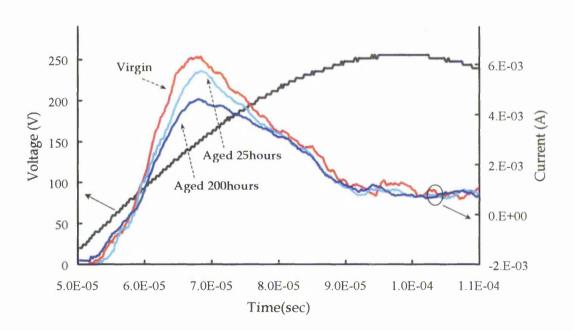

| Figure 6.16 | Tunneling currents response to applied voltage for an ACTFEL device annealed at 600 °C in its virgin, aged for 25 and 200 hours in vacuum       |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

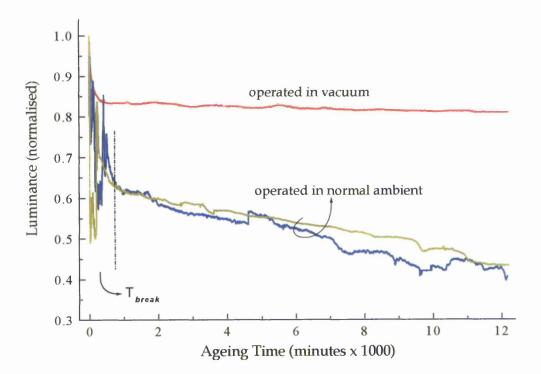

| Figure 6.17 | EL luminance as a function of operation time for ACTFEL device annealed at 400 $^\circ$ C, operated in normal ambient and in vacuum             |

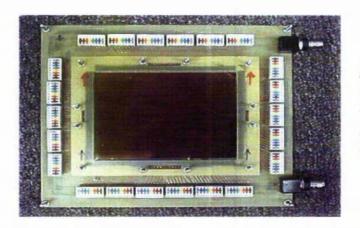

| Figure 6.18 | Picture of the custom-made measurement rig utilised for testing a commercial ACTFEL quarter VGA display panel                                   |

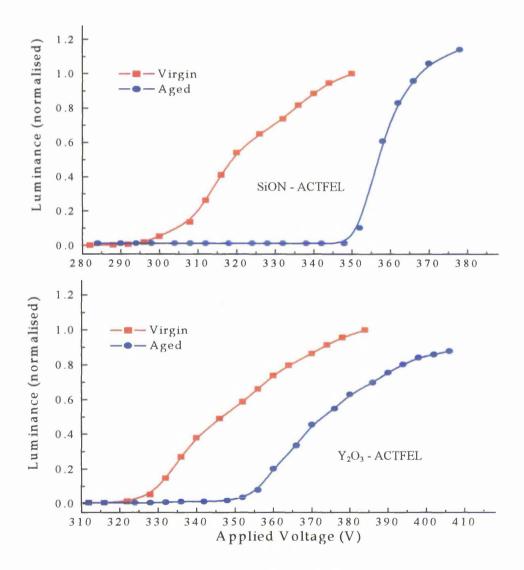

| Figure 6.19 | LV characteristics for ACTFEL devices with SiON insulator and $Y_2O_3$ insulator in its virgin and aged state                                   |

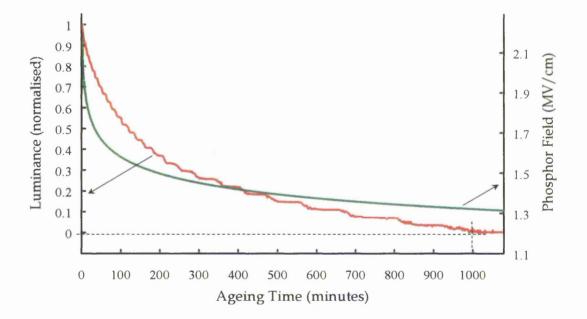

| Figure 6.20 | Phosphor field and luminance characteristics as a function of ageing time for SiON ACTFEL device                                                |

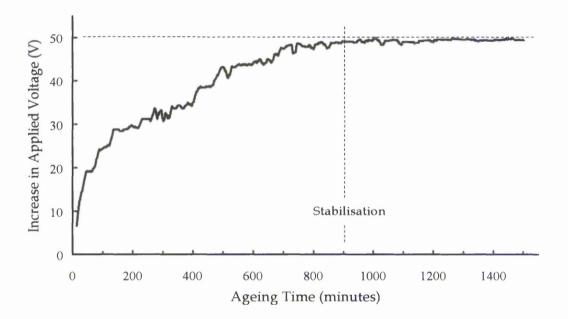

| Figure 6.21 | Plot of the increase in applied voltage that was required to maintain SiON ACTFEL device luminance at a fixed level                             |

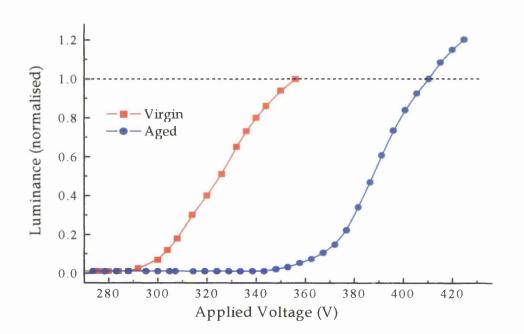

| Figure 6.22 | LV characteristics for SiON ACTFEL device in its virgin state and electrically aged by gradual increase in voltage state                        |

| Figure 6.23 | Luminance as a function of phosphor field for SiON ACTFEL device in its virgin state and electrically aged by gradual increase in voltage state |

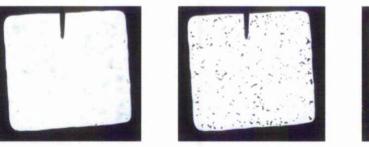

| Figure 6.24 | Pictures of an ACTFEL device annealed at 400 °C with ITO top electrode taken at various times during ageing                                     |

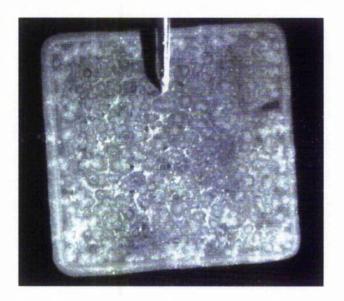

| Figure 6.25 | Picture of an ACTFEL device with ITO top electrode after being operated for 15 hours                                                            |

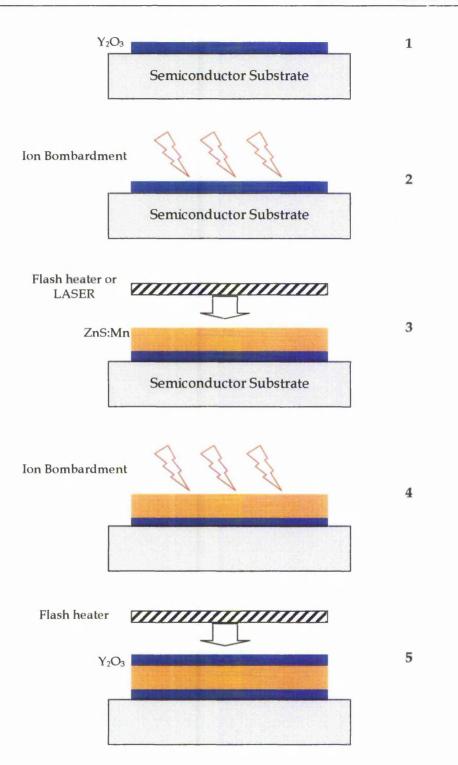

| Figure 7.1  | The fabrication route proposed by the author for engineering an optimised ACTFEL device                                                         |

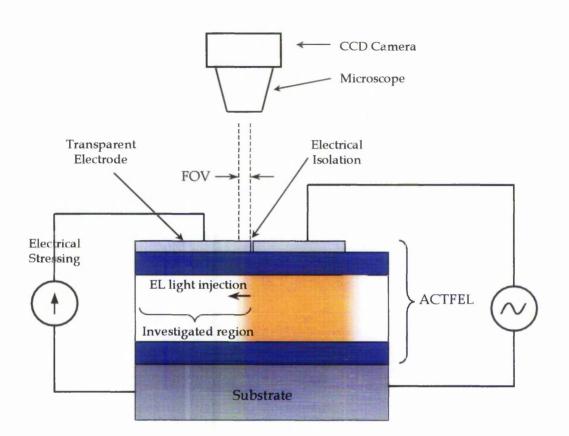

| Figure 7.2  | Schematics of the CCD image capture configuration, which could be utilised to investigate decay of luminance as a function of material length   |

| Figure 7.3  | Possible image captured of a test ACTFEL structure showing luminance decay as a function of material length                                     |

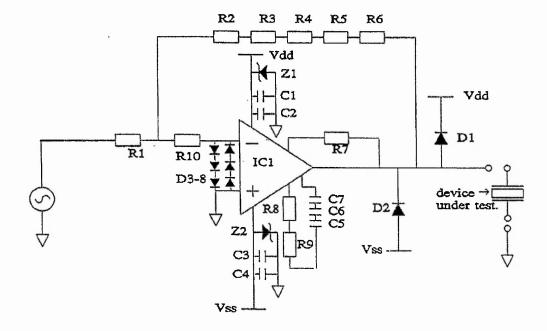

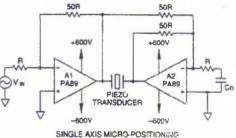

| Figure A.1  | Circuit diagram of the High Voltage Amplifier used for operating the ACTFEL devices                                                             |

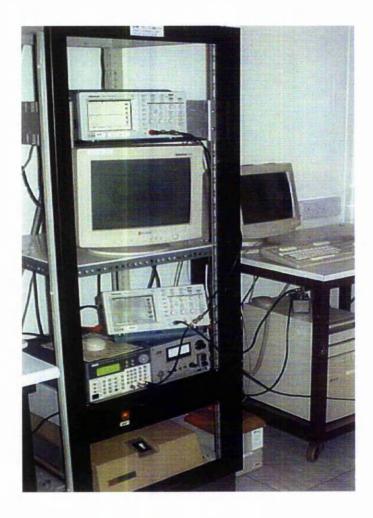

| Figure B.1  | Programmable control system utilised for the probe station described in section 2.4.1 and the vacuum measurement unit described in 2.5          |

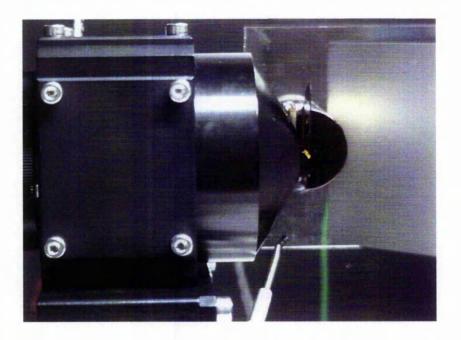

| Figure B.2  | Microscope attachment used in the Agema thermal imaging system described in section 2.4.4 to image an active area of 1 mm diameter              |

|             |                                                                                                                                                 |

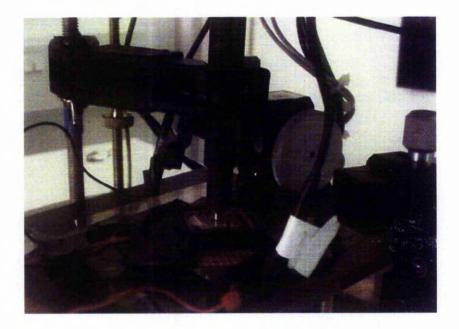

| Figure B.3 | The fibre optic system for vertical out EL emission ACTFEL device                                                              |

|------------|--------------------------------------------------------------------------------------------------------------------------------|

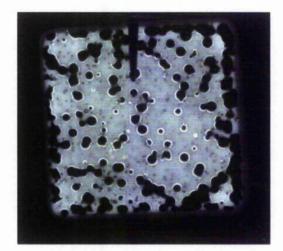

| Figure D.1 | ITO top electrode ACTFEL device with islands of non-active regions due to selective breakdown                                  |

| Figure D.2 | ITO top electrode ACTFEL device completely broken down with snake<br>like chain indicating the affected area due to high field |

| Figure D.3 | Al top electrode ACTFEL device showing a virgin device and the device with regions of selective breakdown                      |

| Figure D.4 | Al top electrode ACTFEL device, showing peeling of the Al electrode layer after ageing                                         |

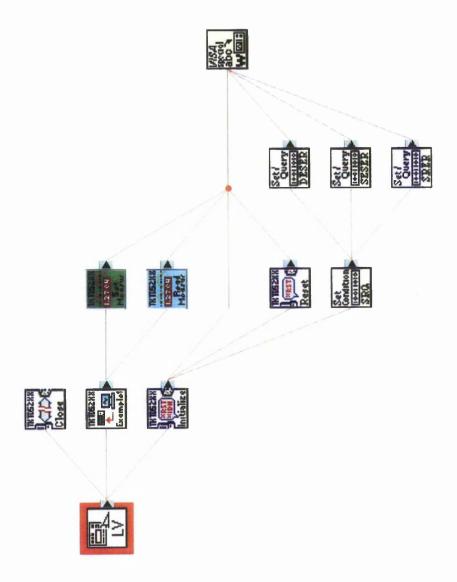

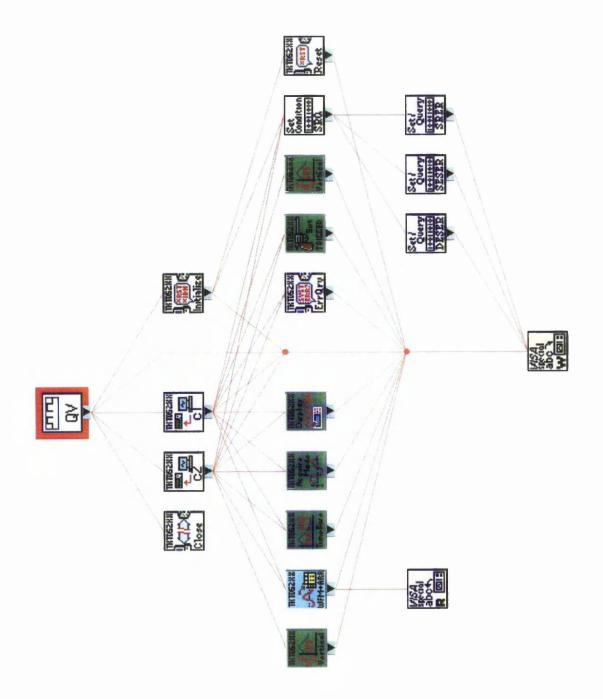

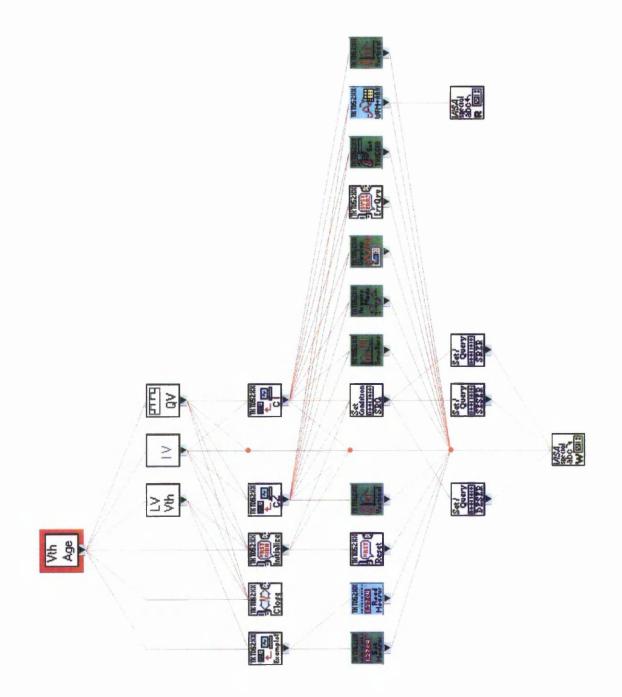

| Figure E.1 | Labview subroutine hierarchy Luminance versus Voltage measurement diagram                                                      |

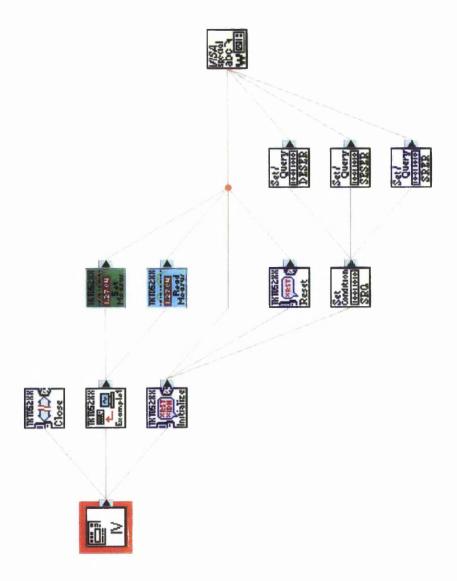

| Figure E.2 | Labview subroutine hierarchy Transferred Charge versus Voltage measurement diagram                                             |

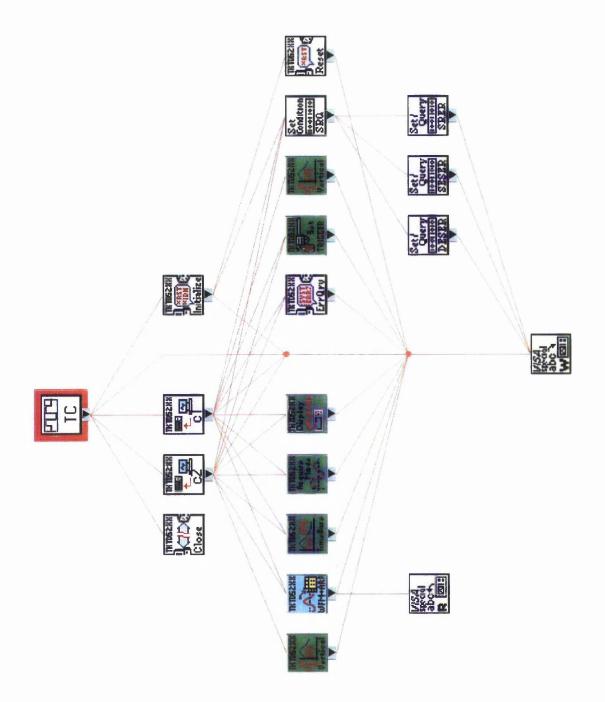

| Figure E.3 | Labview subroutine hierarchy Current versus Voltage measurement diagram                                                        |

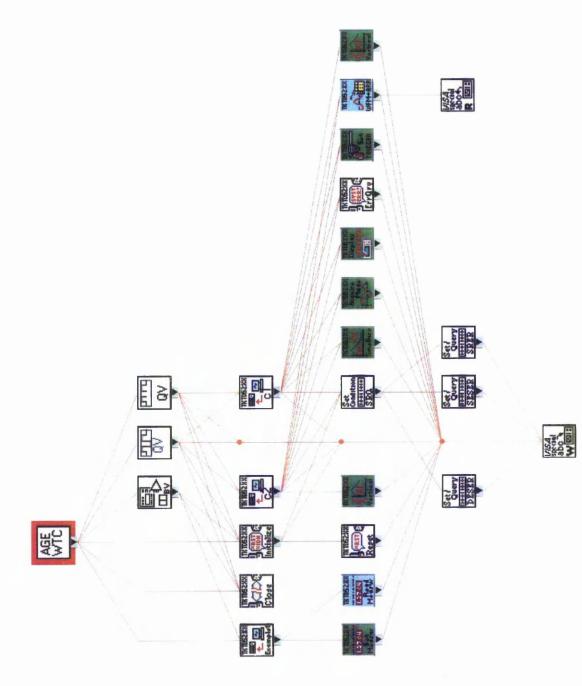

| Figure E.4 | Labview subroutine hierarchy Transient Capture measurement diagram                                                             |

| Figure E.5 | Labview subroutine hierarchy Ageing with LV measurement diagram                                                                |

| Figure E.6 | Labview subroutine hierarchy Automatic voltage increase measurement diagram                                                    |

### List of Tables

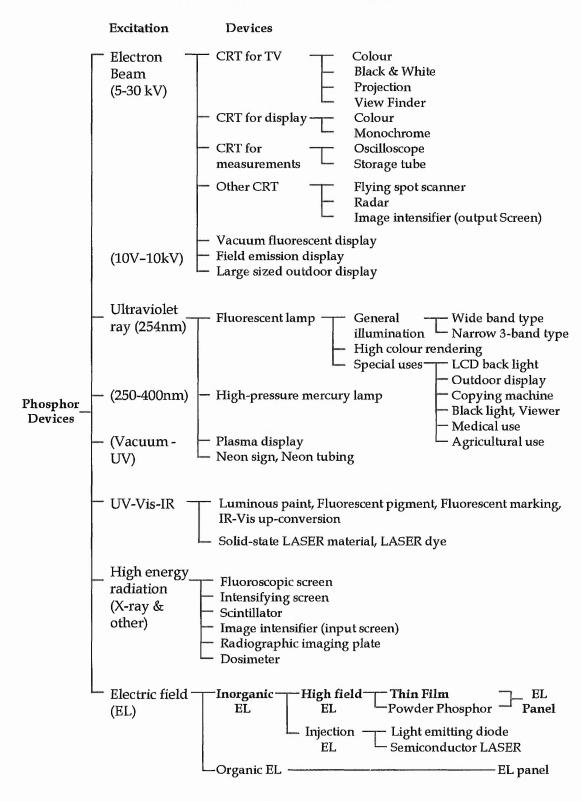

| Table 1.1 | Phosphor devices and application                                                                                                         |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| Table 1.2 | Summary of dielectric and optical properties for some insulators material, which could be used in ACTFEL device construction             |

| Table 3.1 | Summary of the average breakdown strength for thin film $Y_2O_3$ using AC and DC electrical breakdown technique                          |

| Table 5.1 | List of the expected diffraction lines in XRD patterns of ZnS:Mn                                                                         |

| Table 6.1 | Summary of the calculated pre-clamping interface state charge from measured CV data for ACTFEL device annealed at different temperatures |

| Table A.1 | List of components used in the High Voltage Amplifier circuit design                                                                     |

### List of Abbreviations

| А                              | Ampere                                                  |

|--------------------------------|---------------------------------------------------------|

| AC                             | Alternating Current                                     |

| ACTFEL                         | Alternating Current Thin Film Electroluminescent        |

| Al <sub>2</sub> O <sub>3</sub> | Aluminium Oxide                                         |

| Al                             | Aluminium                                               |

| a.u.                           | Arbitrary Units                                         |

| BaTiO₃                         | Barium Titanate                                         |

| BaSrTiO₃                       | Barium Strontium Titanate                               |

| °C                             | Degree Celsius                                          |

| CATS                           | Computer Aided Thermograph Software                     |

| CCD                            | Charge Couple Device                                    |

| CRT                            | Cathode Ray Tube                                        |

| CSC                            | Charge Storage Capacity                                 |

| CV                             | Capacitance versus Voltage                              |

| DC                             | Direct Current ,                                        |

| DCTFEL                         | Direct Current Thin Film Electroluminescent             |

| EL                             | Electroluminescence                                     |

| eV                             | Electron-Volts                                          |

| FWHM                           | Full Width at Half Maximum                              |

| FOV                            | Field Of View                                           |

| GPIB                           | General Purpose Interface Bus                           |

| $H_2$                          | Hydrogen                                                |

| $H_2S$                         | Hydrogen Sulphide                                       |

| HV                             | High Voltage                                            |

| IV                             | Current versus Voltage                                  |

| ITO                            | Indium Tin Oxide                                        |

| LASER                          | Light Amplification by Stimulated Emission of Radiation |

| LDB                            | Localised Destructive Breakdown                         |

| LETFEL                         | Laterally Emitting Thin Film Electroluminescent         |

| LV                             | Luminance versus Voltage                                |

|                                |                                                         |

### List of Abbreviations

| MIS                             | Metal Insulator Semiconductor                     |

|---------------------------------|---------------------------------------------------|

| MOS                             | Metal Oxide Semiconductor                         |

| Mn                              | Manganese                                         |

| MOSFET                          | Metal Oxide Semiconductor Field Effect Transistor |

| N.A.                            | Numerical Aperture                                |

| NTU                             | Nottingham Trent University                       |

| O <sub>2</sub>                  | Oxygen                                            |

| OpAmp                           | Operational Amplifier                             |

| рА                              | Pico Ammeter                                      |

| PMT                             | Photo Multiplier Tube                             |

| PC                              | Personal Computer                                 |

| PL                              | Photoluminescence                                 |

| QV                              | Charge versus Voltage                             |

| Si                              | Silicon                                           |

| Si <sub>3</sub> N <sub>4</sub>  | Silicon Nitride                                   |

| SiO <sub>2</sub>                | Silicon Dioxide                                   |

| SiO <sub>x</sub> N <sub>y</sub> | Silicon Oxynitride                                |

| SO <sub>2</sub>                 | Sulphur Dioxide                                   |

| $Ta_2O_5$                       | Tantalum Oxide                                    |

| TFEL                            | Thin Film Electroluminescent                      |

| UPS                             | Uninterruptible Power Supply                      |

| UV                              | Ultra-Violet                                      |

| wt%                             | Weight percentage                                 |

| XRD                             | X-Ray Diffraction                                 |

| Y                               | Yttrium                                           |

| $Y_2O_3$                        | Yttrium Oxide                                     |

| ZnO                             | Zinc Oxide                                        |

| ZnN                             | Zinc Nitride                                      |

| ZnS                             | Zinc Sulphide                                     |

| ZnS:Mn                          | Zinc Sulphide doped with Manganese                |

|                                 |                                                   |

| A                | Angstrom                                      |

|------------------|-----------------------------------------------|

| А                | Area                                          |

| a                | Lattice constant                              |

| α                | Phosphor field ratio                          |

| aop              | Light attenuation coefficient                 |

| x                | Semiconductor electron affinity               |

| cm               | Centimetre                                    |

| Cacc             | Accumulation capacitance                      |

| с                | Velocity of light (3 x 10 <sup>8</sup> m/sec) |

| Cfb              | Flatband capacitance                          |

| C <sub>FBS</sub> | Silicon surface capacitance at flatband       |

| Ci               | Insulator layer capacitance in ACTFEL device  |

| Cins             | Thin film insulator layer capacitance         |

| Cinv             | Inversion capacitance                         |

| Cm               | MIS diode capacitance                         |

| C <sub>p</sub>   | Phosphor layer capacitance in ACTFEL device   |

| Cs               | Silicon surface capacitance                   |

| Cse              | Sense Capacitance                             |

| Ct               | ACTFEL capacitance                            |

| o                | Degree                                        |

| ΔC               | Change in capacitance                         |

| ΔV               | Change in voltage                             |

| d                | Thickness                                     |

| d <sub>hki</sub> | Plane spacing                                 |

| di               | Distance between two charges                  |

| d <sub>p</sub>   | Phosphor layer thickness                      |

| D <sub>it</sub>  | Density of interface state traps              |

| εi               | Permittivity of the insulator                 |

| ε <sub>r</sub>   | Relative dielectric constant                  |

|                  |                                               |

| εσ               | Permittivity of vacuum (8.85 x $10^{-12}$ F/m)                                  |

|------------------|---------------------------------------------------------------------------------|

| ε <sub>S</sub>   | Permittivity of Silicon (11.9 x ₅₀)                                             |

| Е                | Energy                                                                          |

| E <sub>bd</sub>  | Breakdown field                                                                 |

| E <sub>F</sub>   | Fermi level                                                                     |

| Ei               | Intrinsic Fermi level                                                           |

| E <sub>th</sub>  | Phosphor threshold field                                                        |

| F                | Farad                                                                           |

| F <sub>P</sub>   | Field across the phosphor layer                                                 |

| γ                | Charge distribution factor                                                      |

| h                | Plank's constant ( $4.1 \times 10^{-15} \text{ eV}$ sec)                        |

| hkl              | Miller indices                                                                  |

| i(t)             | Instantaneous current                                                           |

| I <sub>dis</sub> | Current induced by ACTFEL device capacitance                                    |

| I <sub>ext</sub> | Externally measured current                                                     |

| Io               | Maximum intensity                                                               |

| IT               | Tunneling current                                                               |

| k                | Boltzmann's constant ( $1.4 \times 10^{-23} \text{ j/K}$ )                      |

| kHz              | Kilohertz                                                                       |

| λ                | Wavelength                                                                      |

| $\lambda_n$      | Debye length                                                                    |

| L                | Luminance                                                                       |

| μ                | Dipole moment                                                                   |

| μC               | Micro-Coulomb                                                                   |

| mm               | Millimetre                                                                      |

| MV               | Mega-Volt                                                                       |

| η                | Efficacy                                                                        |

| n                | Refractive Index                                                                |

| ni               | Intrinsic Silicon carrier concentration $(1.45 \times 10^{10} \text{ cm}^{-3})$ |

|                  |                                                                                 |

| nm               | Nanometre                                                      |

|------------------|----------------------------------------------------------------|

| Na               | Donor doping density                                           |

| φm               | Metal work function                                            |

| φms              | Work function difference between metal and semiconductor       |

| φs               | Semiconductor work function                                    |

| ψs               | Silicon surface potential                                      |

| Р                | Power / dielectric polarisation                                |

| q                | Charge on the electron $(1.6 \times 10^{-19} \text{ coulomb})$ |

| q(t)             | Instantaneous charge                                           |

| Q                | Charge                                                         |

| Q <sub>ext</sub> | Externally measured charge                                     |

| Qf               | Oxide fixed charge                                             |

| Q <sub>int</sub> | Pre-clamping interface charge                                  |

| Qit              | Interface state charge                                         |

| Qm               | Mobile ionic charge                                            |

| Qot              | Oxide trap charge                                              |

| Qs               | Silicon surface charge                                         |

| R                | Resistance                                                     |

| θ                | Angle                                                          |

| $\theta_i$       | Incident angle                                                 |

| $\theta_t$       | Transmission angle                                             |

| τ <sub>p</sub>   | Photoluminescent decay constant                                |

| t                | Crystallite size                                               |

| Т                | Temperature                                                    |

| V                | Voltage                                                        |

| V <sub>bd</sub>  | Breakdown voltage                                              |

| Vfb              | Flatband voltage                                               |

| V <sub>G</sub>   | Gate Voltage                                                   |

| Vins             | Voltage across the insulator                                   |

|                  |                                                                |

| VTFEL           | Voltage across TFEL device |

|-----------------|----------------------------|

| V <sub>th</sub> | Threshold voltage          |

| Wm              | Maximum depletion width    |

| x               | Material length            |

Research is to see what everybody else has seen and to think what nobody else has thought.

Albert Szent-Gyorgyi

To my mother, for everything she has done for me

Performance Studies of Thin Film Electroluminescent (TFEL) Devices CHAPTER 1: Introduction

### **CHAPTER 1**

#### **INTRODUCTION**

#### 1.1 Electroluminescence

Electroluminescence is a process by which a material generates non-thermal radiation from the excitation of an electron<sup>1</sup>. In 1752, Benjamin Franklin showed this phenomenon caused by electrical discharge occurring on a grand scale in lightning<sup>2</sup>. This method of producing <u>cold light</u> occurs from the excitation of high-energy electrons reacting with a substance, which is unlike the conventional black body radiation from an incandescent tungsten filament. In 1936, French physicist, Destriau observed such light was emitted from the phosphor compound, Zinc Sulphide when a high electric field was applied<sup>3</sup>. This mechanism of producing light has been the basis of many modern phosphor based information displays. The various kinds of phosphor devices and by the manner the phosphor is applied are given in Table 1.1. With the advancement of thin-film process technology in the 1960's and the introduction of a stable Electroluminescence display panel design in 1974<sup>4</sup>, a significant amount of the more recent display development efforts has been directed to Thin Film Electroluminescent devices<sup>5</sup>. However, the nature of the device characteristics requires more understanding than that which is available presently, for further improvement to push this technology forward among its rivals.

#### Performance Studies of Thin Film Electroluminescent (TFEL) Devices CHAPTER 1: Introduction

1-2

#### 1.2 Alternating Current Thin Film Electroluminescent device

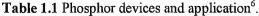

A Thin Film Electroluminescent (TFEL) device can be driven by either Direct Current (DC) or Alternating Current (AC). This work focuses on the Alternating Current Thin Film Electroluminescent (ACTFEL) device. This Optoelectronic device is very amenable for manufacturing lightweight, wide viewing angle, solid state, bright, high-contrast and pleasant to the eye emissive flat-panel display. A typical ACTFEL structure is shown in Figure 1.1.

Light Emission from Device

Figure 1.1 Schematic of a typical Alternating Current Thin Film Electroluminescent device<sup>4</sup>.

It consists of an active light emitting thin film phosphor, sandwiched between thin film dielectric claddings and electrodes<sup>7,8,9</sup>. Light is emitted from this double-insulator Electroluminescence (EL) device when voltage above threshold (V<sub>th</sub>) of alternating polarity is applied between the Indium Tin Oxide (ITO) and the top Aluminium (Al) electrodes. Majority of the light produced exits vertically through the ITO electrode. No light is emitted from the Al electrode side as most light would be scattered and reflected from its mirror-like interface.

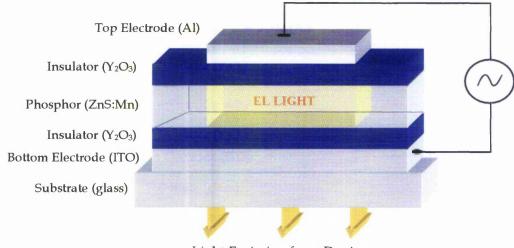

The phosphor is typically a wide-bandgap semiconductor doped with an activator material<sup>10</sup>. Emission colour can be tuned by doping with different materials. In this study, the phosphor host material is Zinc-Sulphide (ZnS), which is doped with Manganese (Mn). The dopant acts as an activator to produce yellow-orange light<sup>11</sup>, centered at 585nm in the visible spectrum with a spectral bandwidth of 40nm<sup>5</sup>. The ZnS:Mn host-dopant combination is the most efficient phosphor<sup>6,12</sup>, to date. The EL mechanism can be described with the energy-band diagram of the ACTFEL device<sup>13,14</sup> as shown in Figure 1.2.

Figure 1.2 Energy-band diagram of the double-insulating-layer-type ACTFEL device, shown for a single polarity. (1) electrons are injected from the interface states by high-field-assisted tunneling. (2) electron accelerates and gains kinetic energy due to applied field. (3) impact-excitation of manganese luminescent centres, which then cause radiative transition. (4) electrons travel through the phosphor to be trapped at the anode phosphor-insulator interface.

The primary source of electrons is located at the ZnS, phosphor-insulator interface, known as interface states<sup>4,13,14,15</sup>. Electrons are injected from the interface states into the conduction band<sup>16</sup> of the phosphor at applied voltage above V<sub>th</sub> or field across the phosphor layer in excess of  $10^8$  V/m by high-field-assisted tunneling<sup>17,18</sup>.

The alternating voltage on the electrode causes an alternating electric field in the insulator and phosphor layer. Due to the electric field in the phosphor layer, injected electrons are accelerated and gain sufficient kinetic energy to become <u>hot electrons</u> to excite luminescent centres. Excitation is a result of direct impact by hot electrons with activator ions (Mn<sup>++</sup>) located at luminescent centres. Light is emitted as the activator ions relax from an excited state<sup>13</sup>. Travelling electrons along the phosphor layer, are finally trapped at the phosphor-insulator interface states on the anode side, causing polarisation. When the polarity of the alternating voltage is reversed, the process is repeated in the opposite direction. The interface states serve not only to emit electrons but also to receive and store them<sup>19</sup>. The near-interface polarisation assists the overall field in the next cycle.

Each of the processes described above are essential for the continuous operation of the thin film structure to generate light. In an ideal ACTFEL device, under normal operating condition, these processes should take place without changes in device characteristics, efficiency or operation parameters. The light emission from a TFEL device is given by

$$\mathbf{L} = \eta \mathbf{P}$$

Eq. 1.1

where L is the flux in lumens,  $\eta$  is the efficiency in lumens per watt and P is the power dissipated in generating the light. The factors concerning the efficiency are directly related to the engineering of this device. In addition previous study and experiments undertaken for this work demonstrates that brightness degradation and device failure occurs during device ageing, hence reducing efficiency. A review of the potential phenomena responsible for determining the device efficiency and reduction in the performance of ACTFEL device is detailed in the following section.

# **1.3 Review of EL Performance Mechanisms**

#### 1.3.1 Material Properties

As discussed previously, the ACTFEL device consists primarily of a phosphor film sandwiched between two insulators. In this study, ZnS:Mn, phosphor and Yttrium Oxide (Y<sub>2</sub>O<sub>3</sub>), insulator were mainly used. These materials are deposited using radio frequency magnetron sputtering. Structural analysis has shown that these thin films grown on single crystal (100) silicon wafer using this growth technique are polycrystalline<sup>20,21</sup>. The quality of the crystalline structure of each individual layer grown one on top of another is believed to be dependent upon the base layer used for deposition. Also, fabrication conditions such as growth temperature<sup>22,23</sup>, and post deposition annealing<sup>24</sup> affects the thin film material properties.

A polycrystalline structure does impose difficulties in distinguishing fundamental Localised Destructive Breakdown (LDB) from those relating to material artefacts such as grain boundaries and other layer inhomogeneities. A phosphor layer sandwiched by two electrodes is the simplest of an EL device. This type of structure is a typical Direct Current Thin Film Electroluminescent (DCTFEL) device and is the building block of an ACTFEL device. The ZnS:Mn, phosphor layer at low applied field, has high resistivity and is essentially an insulator. Above a critical field, typically between 0.5 and 2.0 MV/cm, current increases rapidly with voltage and simultaneously electroluminescence is observed. Therefore non-uniformity of the layer would pose a serious design flaw, with different threshold voltages. Additionally, non-uniformity would also result in high field region more vulnerable to tunnel breakdown<sup>25</sup>. Study on DCTFEL devices has revealed that the nature of the breakdown event itself and of the associated damage does seem to depend on the crystal quality of the ZnS:Mn layer<sup>26</sup>.

The encapsulation with insulators on either side of the phosphor layer forms a capacitive ACTFEL device. The insulator layer is a series capacitor to the phosphor layer with a fraction of the applied voltage dropping across the insulators. Therefore the insulator capacitance will influence the threshold voltage for tunnelling to occur. The

insulators do also provide the current limitation necessary for preventing device failure during normal operation and hence plays an important role in prolonging operating lifetime. Since the insulating material is directly related to the stability of the ACTFEL device<sup>27</sup> it is therefore important to select a high-quality dielectric material for optimum engineering of this device.

The preferred parameters for the insulator are high dielectric constant and breakdown strength, desirable insulator/phosphor electronic interface properties<sup>28</sup>, low leakage current<sup>29</sup> in the order of picoAmpere at the operating voltage, stable electro-optical properties during operation and suitable refractive index. It is also important to have a good structural coordination (adhesion) between the insulating layers and the emitting layer<sup>28,30</sup>. In Table 1.2, a summary of the important parameters for some insulators found in literature is given. The table contains a list of materials, which could be used in the construction of ACTFEL devices.

| Material                        | Refractive<br>Index | Energy Bandgap<br>(eV) | Breakdown<br>Strength (MV/cm) | Relative<br>Dielectric<br>Constant |

|---------------------------------|---------------------|------------------------|-------------------------------|------------------------------------|

| SiO <sub>2</sub>                | 1.4 – 1.5           | 8.9                    | 10                            | 3.9                                |

| SiO <sub>x</sub> N <sub>y</sub> | 1.5 – 2.1           | 5.1                    | 9 - 26                        | 3.9 - 7                            |

| Al <sub>2</sub> O <sub>3</sub>  | 1.5                 | 8.7                    | 7                             | 8.5 - 10                           |

| Ta <sub>2</sub> O <sub>5</sub>  | 2.2 - 2.5           | 4.2                    | 4.5                           | 25                                 |

| Y <sub>2</sub> O <sub>3</sub>   | 1.9                 | 5.5                    | 3.85                          | 10 - 18                            |

| Si <sub>3</sub> N <sub>4</sub>  | 2.1                 | 5.1                    | 10                            | 7.5                                |

| BaTiO₃                          | 2.4                 | 2.5 - 3.9              | 0.42                          | 300 - 2000                         |

| SrTiO₃                          | 1.9 – 2.2           | 3.6                    | 0.3 - 4                       | 150 - 400                          |

| BaSrTiO <sub>3</sub>            | 2.1 -2.4            | 3.2 - 4                | 4                             | > 870                              |

Table 1.2 A summary of dielectric and optical properties for some insulators material, which could be used in ACTFEL device construction<sup>28,31,32</sup>. The values given are a guideline only because it depends on the deposition parameters.

The crystal structure, light attenuation coefficient and refractive index of the layers are important factors for optical light propagation within an ACTFEL device. This property of the device is explained in Chapter 2. It has been reported that sputtered phosphor films produce disordered polycrystalline columnar structures<sup>33</sup>. Also, the mean grain size of the thin film increases when post-deposition annealing is performed above 450°C, which induces higher saturation brightness<sup>34,35,36</sup>. Therefore, it was an important aspect of this research to correlate the crystalline properties of the thin film with the Electro-Optical behaviour of the ACTFEL device.

Light emission from the phosphor is a cause of direct impact by energetic electrons with activator ions located in favourable location. Generally Mn<sup>++</sup> ions sit as isoelectronic substitute on a Zn site in the ZnS lattice, to maintain charge neutrality. These sites could potentially become luminescent centres. In an as deposited phosphor film, these locations are initially associated with defects. It has been demonstrated that following an annealing process these ions become located in a more beneficial Zn-vacancies in the crystal lattice to form a more efficient luminescent centres<sup>24,36</sup>. This is evidenced by an increase in saturation brightness and a reduction in the number of non-radiative decay centres, deduced from the increase in decay time constant. Consequently the effect of Mn incorporation with host ZnS lattice as a function of annealing temperature would be an important factor for consideration, which is discussed in Chapter 5.

Two causes of degradation due to the material could be either bulk electron traps within the phosphor or traps associated with interface states. Interface states are presently the primary source of charge, however such states may well be a principal cause of weakness particularly under high field stressing. Some have avoided the use of interface states by utilising injection layers<sup>12</sup>, however, these pose new fabrication challenges. It was also found that the chemical volatility between the phosphor and insulator material near the interface causes instability of device characteristics<sup>37,38</sup>. Therefore the study on changes at the interface, which lead to reduction in the efficiency of the device, was carried out. Various techniques are used to relate the effect of these trap properties on device performance, which is presented in Chapter 6. The optimum Mn concentration for use in ZnS host material is an important parameter to produce a high brightness device<sup>13,39</sup>. In this respect, degradation in crystallinity was observed when the Mn concentration is too high<sup>40,41</sup>, which would reduce device brightness. Additionally, at high Mn concentrations, a "red wing" at about 600-620 nm would appear in the spectrum, causing a shift of the peak wavelength towards longer wavelenghts<sup>5</sup>. This is not desirable in certain applications and could also cause instability in the spectrum during operation. Fabrication temperature has been reported to also have an influence on the actual Mn concentration incorporated in the deposited phosphor film<sup>40,42</sup>.

It has been suggested that electrons travelling through the phosphor take certain preferred paths<sup>42,43</sup>. It is believed that a preferred path is the result of inhomogeneities in the phosphor layer; also irregularities in the insulator-phosphor interface that cause high field regions where electrons are preferentially emitted. The electrons will excite and exhaust the Mn radiative sites along this route thus reducing the efficiency of the phosphor film. Thus heterogeneity of the Mn distribution maybe a possibility for current non-uniformity within the phosphor layer<sup>35</sup>. Hence structural study was performed on the thin film to provide a better understanding on the influence of the factors that cause the device breakdown and degradation characteristics, presented in Chapters 5 and 6.

Additionally, sulphur vacancies are believed to be responsible for many instabilities in the phosphor. This type of vacancy is believed to produce space charges forming defects in the bulk of ZnS. However, this type of defect can be reduced with the introduction of H<sub>2</sub>S in the growth and annealing process, which has demonstrated a promise towards this goal<sup>44</sup>. The existence of space charge could alter device electrical characteristics during operation and may act as a degradation mechanism.

The ACTFEL device is fabricated as a non-aged device structure allowed by the process route designed. When the device is operated by the application of electric field, various changes continuously takes place during its lifetime. The factors, which could influence the device characteristics, will be discussed in the next section.

# 1.3.2 Effects of Electric Field

The ACTFEL device operates with electric fields in the order of 10<sup>8</sup> V/m. Any imperfections in the thin film phosphor or insulators could cause a short between the electrodes and a destructive current of high amplitude to flow through the device. Several types of breakdown are possible due to instabilities within the electrodes. These breakdowns arise mainly from micro breakdowns, which are related to thermal runaway or electronic avalanching within the dielectric layer<sup>35</sup>. Evidence for this is the appearance of arcing propagating as filaments, which travel across the aluminium electrode.

Dielectric breakdown in thin films is one effect of a catastrophic failure of the device and was given priority in the study. This study is important for constructing high efficiency TFEL device<sup>45,46</sup> since it provides an understanding of the maximum field that can be applied to the device before breakdown occurs.

Electroluminescence occurs in a TFEL device when voltage above threshold is applied between the cathode and anode of the device as illustrated in Figure 1.1. The inner field at the cathode interface influences the supply of primary carriers, which determines device brightness. The applied voltage controls the inner phosphor field by the capacitance division ratio between the phosphor and insulator layer. Hence changes in this ratio during operation will shift the Luminance versus Voltage characteristic rigidly along the voltage axis<sup>47,48,49</sup>. However this shift was found not to change the luminance versus input power characteristics<sup>4</sup>. Nevertheless the operating characteristics of the ACTFEL would be influenced. The degree of this degradation effect depends on the type of dielectric material utilised<sup>28,50</sup>. Hence the stability of the electrical properties of the phosphor and insulator layer during operation is very important. It has been reported that atomic rearrangement taking place in the ZnS:Mn layer on the application of high field, alters the device characteristics during the beginning of the ageing process<sup>51</sup>.

Polarisation near the interface is also an important part in the operation of an ACTFEL device. The phosphor/insulator interface injects high-energy electrons into the bulk by

high-field–assisted tunnelling. Under AC operation, at the end of each cycle an accumulation of charge occurs at the opposite interface of the device. These charges will be trapped into the interface traps creating a momentary internal polarisation near the interface. This phenomenon is an important characteristic as it increases the effective electric field, thus increasing the overall efficiency of the device in the next cycle<sup>7,47</sup>. However, due to continuous impact of high-energy electrons at the interface, either changes to the interface states or a redistribution of traps could occur; thus influencing the efficiency of this operating mechanism.

The presence of electron traps in the form of sulphur vacancies due to non-stoichiometry between the Zinc and Sulphur of the phosphor material will also influence the electrical behaviour of the device. There is some evidence suggesting that the trap distribution can change over time and hence affect device characteristics. Furthermore, the sulphur vacancies associated with donor traps facilitate Poole-Frenkel emission, in addition to the usual tunnelling from interface states<sup>48</sup>. Hence a reduction occurs in the number of hot electron and the overall luminance of the device. Unpaired Zinc, Sulphur or impurity atoms create isolated ions within the bulk of the phosphor layer and these charges could migrate due to the application of electric field. An accumulation of positive charges at the interface could occur due to continuous device operation. Isolated charge migration has been found to cause asymmetrical device behaviour after some ageing<sup>52,53,54</sup>. Methods of eliminating or reducing sulphur vacancies for example as discussed previously should be of importance in the process of producing TFEL display devices with improved degradation characteristics.