# FOR REFERENCE ONLY

### The Nottingham Trent University Library & Information Services SHORT LOAN COLLECTION

| Date    | Time | Date        | Time |  |

|---------|------|-------------|------|--|

|         |      |             |      |  |

| Sin Sin |      |             |      |  |

| 12 JUL  |      |             |      |  |

|         |      |             |      |  |

|         |      |             |      |  |

|         |      |             |      |  |

|         |      |             |      |  |

|         |      |             |      |  |

|         |      |             |      |  |

|         |      | Salar Salar |      |  |

HIS ITEM MAY NOT BE RENEWED

ProQuest Number: 10183226

All rights reserved

INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

ProQuest 10183226

Published by ProQuest LLC (2017). Copyright of the Dissertation is held by the Author.

All rights reserved.

This work is protected against unauthorized copying under Title 17, United States Code Microform Edition © ProQuest LLC.

ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 – 1346

## INTEGRATED FAULT TOLERANCE FOR PACKET-SWITCHED NETWORKS

### **ROBIN HOTCHKISS**

A thesis submitted in partial fulfilment of the requirements of The Nottingham Trent University for the degree of Doctor of Philosophy

Department of Electrical and Electronic Engineering The Nottingham Trent University Burton Street Nottingham United Kingdom NG1 4BU

October 2000

#### ABSTRACT

A novel VLSI hardware packet routing switch, integrating fault tolerant mechanisms, has been developed. The device can be used to construct an embedded parallel or distributed processing architecture.

A review of packet switched techniques has been carried out, leading to a high-level specification for a next generation packet switched network. From this specification, an eight-link router-switch has been implemented in a programmable logic device, which significantly enhances the primary routing features compared to earlier devices.

The distributed fault tolerance features were implemented in two stages. The first stage is concerned with critical interruption of the link stability, which has been proven through simulation and hardware verification. The first stage features detected and localised the effects of network failure, while supplying features to reduce link activity where required. The second deals with deadlock detection and recovery, which investigated a detection method that minimised time and false detections irrespective of network traffic. The investigative second stage has been verified by simulation.

This work successfully culminated in the production of a fault tolerant hardware routing switch. All basic routing features of the device operation have been proven through simulation and hardware testing. Simulations have been used to subject the device to a range of extended workloads for confidence of operation. The router-switch supports the network specification for a fault tolerant network, based on a distributed mechanism, allowing a linear scaling factor for tolerance to failure as the network is modified. This maximises network availability in the presence of faults. Key features of the design were compared and contrasted with the current state of the art in the literature.

#### ACKNOWLEDGEMENTS

I would like to thank the following people for all the help and support they have provided over the duration of my studies. My supervisors Prof. BC O'Neill and Dr. S Clark; my colleagues and friends Dr. GC Coulson, Dr. RH Day, Mr D Downes, Mr JH Ng, Mr. C Oswald, Dr. RM Ranson, and Dr. KL Wong; all my family and other friends, but especially to Mr C Dixon, Mr & Mrs Kaveney-Davis, Mr R Harris, Mr D Moore, and Mrs D Scholey; Mr A Whitehouse who gave me the reference to get me here in the first place.

Finally, I would like to give special thanks to Mr D Corcoran who taught me a great deal in the years of our friendship and was always present with a word of encouragement.

| ABSTRACTI                                                                                    |     |

|----------------------------------------------------------------------------------------------|-----|

| ACKNOWLEDGEMENTS II                                                                          |     |

| TABLE OF CONTENTS III                                                                        |     |

| LIST OF ACRONYMSVI                                                                           |     |

| LIST OF FIGURES VII                                                                          |     |

| LIST OF TABLESIX                                                                             |     |

| 1 INTRODUCTION                                                                               | 1   |

| 1.1 PARALLEL CONCEPTS                                                                        | 1   |

| 1.1 Parallel Architectures                                                                   |     |

| 1.1.1 Parallel Architectures<br>1.2 EFFECTS OF TECHNOLOGICAL ADVANCEMENTS IN DIGITAL SYSTEMS |     |

|                                                                                              |     |

| 1.3 AIMS OF THIS RESEARCH                                                                    |     |

| 1.4 BREAKDOWN OF THESIS                                                                      | /   |

| 2 BACKGROUND TECHNIQUES, METHODOLOGY AND TERMINOLOGY                                         |     |

| 2.1 THE ISO OPEN SYSTEMS INTERCONNECTION MODEL                                               |     |

| 2.2 REVIEW OF THE METHODOLOGIES OF SWITCHED COMMUNICATION                                    | 11  |

| 2.2.1 Physical Link Layer Considerations                                                     | 11  |

| 2.2.2 Data-Link Layer Considerations                                                         | 14  |

| 2.2.2.1 Token Definitions                                                                    | 14  |

| 2.2.2.2 Flow Control                                                                         | 14  |

| 2.2.2.3 Data Link Fault Tolerance                                                            | 19  |

| 2.2.3 Network Layer Considerations                                                           | 20  |

| 2.2.3.1 Switched Architectures                                                               | 20  |

| 2.2.3.2 Connection Methodologies                                                             | 21  |

| 2.2.3.3 Packet Format                                                                        | 25  |

| 2.2.3.4 Adaptive Routing Techniques                                                          | 26  |

| 2.2.3.5 Routing Decisions                                                                    |     |

| 2.2.3.6 Fault tolerance – Error detection and recovery                                       |     |

| 2.2.3.7 Deadlock                                                                             |     |

| 2.2.4 Transport Layer Considerations                                                         | 40  |

| 3 REVIEW OF EARLIER RESEARCH                                                                 |     |

| 3.1 INTRODUCTION TO EARLIER SYSTEMS                                                          |     |

| 3.1.1 NTRODUCTION TO EARLIER SYSTEMS                                                         |     |

| 3.1.2 ICR-C416                                                                               |     |

| 3.1.3 NTR-M04                                                                                |     |

|                                                                                              |     |

| <i>3.1.4 Contemporary Devices</i>                                                            |     |

|                                                                                              |     |

| 3.1.4.2 Reliable Router                                                                      |     |

| 3.1.4.3 Myrinet                                                                              |     |

| 3.2 PHYSICAL LAYER                                                                           |     |

| 3.3 DATA LINK LAYER                                                                          |     |

| 3.3.1 Token Definitions                                                                      |     |

| 3.3.2 Flow Control                                                                           |     |

| 3.3.3 Fault Tolerance                                                                        |     |

| 3.4 NETWORK LAYER                                                                            | 61  |

|                                                                                              | III |

### TABLE OF CONTENTS

| 2 / 2                                                                                                                                                                                                       | Switched Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 62                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 3.4.2                                                                                                                                                                                                       | Connection Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 62                                                                                                                                            |

| 3.4.3                                                                                                                                                                                                       | Packet Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 64                                                                                                                                            |

| 3.4.4                                                                                                                                                                                                       | Adaptive routing techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 67                                                                                                                                            |

| 3.4.5                                                                                                                                                                                                       | Routing Decisions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 68                                                                                                                                            |

| 3.4.6                                                                                                                                                                                                       | Fault tolerance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                               |

| 3.4.7                                                                                                                                                                                                       | Deadlock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 72                                                                                                                                            |

| 4 DESIG                                                                                                                                                                                                     | N DISCUSSION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 73                                                                                                                                            |

| 4.1 LES                                                                                                                                                                                                     | SONS LEARNT FROM EARLIER RESEARCH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 73                                                                                                                                            |

| 4.2 BA                                                                                                                                                                                                      | SIC ROUTER-SWITCH DEFINITION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                               |

| 4.2.1                                                                                                                                                                                                       | Basic Router-switch Physical Layer Protocol Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                               |

| 4.2.2                                                                                                                                                                                                       | Basic Router-switch Data Link Layer Protocol Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                               |

| 4.2.3                                                                                                                                                                                                       | Basic Router-switch Network Layer Protocol Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                               |

| 4.2.4                                                                                                                                                                                                       | Other Router-switch Features and Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                               |

|                                                                                                                                                                                                             | GE ONE DEVELOPMENT FEATURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                               |

| 4.3.1                                                                                                                                                                                                       | Stage One Physical Layer Protocol Enhancements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                               |

| 4.3.2                                                                                                                                                                                                       | Stage One Data Link Layer Protocol Enhancements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                               |

|                                                                                                                                                                                                             | 1 Link Initialisation Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                               |

| 4.3.3                                                                                                                                                                                                       | Stage One Network Layer Protocol Enhancements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                               |

| 4.3.3.<br>4.3.3.                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                               |

|                                                                                                                                                                                                             | 2 Link Invalidation<br>GE TWO DEVELOPMENT FEATURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                               |

| 4.4 517                                                                                                                                                                                                     | Stage Two Development Peatores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                               |

| 4.4.2                                                                                                                                                                                                       | Stage Two Data Link Layer Protocol Enhancements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                               |

| 4.4.3                                                                                                                                                                                                       | Stage Two Network Layer Protocol Enhancements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 89                                                                                                                                            |

| 4.4.3.                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                               |

| 4.4.3.                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                               |

|                                                                                                                                                                                                             | LED ROUTER-SWITCH DESIGN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                               |

|                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                               |

| 51 RA                                                                                                                                                                                                       | NC SKELETAL SWITCH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 07                                                                                                                                            |

|                                                                                                                                                                                                             | SIC SKELETAL SWITCH<br>Ton-Level Router-Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                               |

| 5.1.1                                                                                                                                                                                                       | Top-Level Router-Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 97                                                                                                                                            |

| 5.1.1<br>5.1.2                                                                                                                                                                                              | Top-Level Router-Switch<br>Link Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 97<br>97                                                                                                                                      |

| 5.1.1                                                                                                                                                                                                       | Top-Level Router-Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 97<br>97<br>101                                                                                                                               |

| 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4                                                                                                                                                                            | Top-Level Router-Switch<br>Link Unit<br>Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 97<br>97<br>101<br>106                                                                                                                        |

| 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4                                                                                                                                                                            | Top-Level Router-Switch         Link Unit         Controller         Exchange         JLT TOLERANCE - STAGE ONE         Stage One Enhancements to the Link Unit                                                                                                                                                                                                                                                                                                                                                                                                                                               | 97<br>97<br>101<br>106<br>107<br>107                                                                                                          |

| 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.2 FAI                                                                                                                                                                 | Top-Level Router-Switch         Link Unit         Controller         Exchange         JLT TOLERANCE - STAGE ONE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 97<br>97<br>101<br>106<br>107<br>107                                                                                                          |

| 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.2 FAI<br>5.2.1<br>5.2.2                                                                                                                                               | Top-Level Router-Switch.         Link Unit.         Controller         Exchange         JLT TOLERANCE - STAGE ONE.         Stage One Enhancements to the Link Unit.         Stage One Enhancements to the Controller         JLT TOLERANCE – STAGE TWO                                                                                                                                                                                                                                                                                                                                                        | 97<br>97<br>101<br>106<br>107<br>107<br>110<br>111                                                                                            |

| 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.2 FAI<br>5.2.1<br>5.2.2                                                                                                                                               | Top-Level Router-Switch         Link Unit         Controller         Exchange         JLT TOLERANCE - STAGE ONE         Stage One Enhancements to the Link Unit         Stage One Enhancements to the Controller         JLT TOLERANCE – STAGE TWO         Stage Two Enhancements to the Link Unit                                                                                                                                                                                                                                                                                                            | 97<br>97<br>101<br>106<br>107<br>107<br>110<br>111<br>111                                                                                     |

| 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.2 FAU<br>5.2.1<br>5.2.2<br>5.3 FAU                                                                                                                                    | Top-Level Router-Switch.         Link Unit.         Controller         Exchange         JLT TOLERANCE - STAGE ONE.         Stage One Enhancements to the Link Unit.         Stage One Enhancements to the Controller         JLT TOLERANCE – STAGE TWO                                                                                                                                                                                                                                                                                                                                                        | 97<br>97<br>101<br>106<br>107<br>107<br>110<br>111<br>111                                                                                     |

| 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.2 FAU<br>5.2.1<br>5.2.2<br>5.3 FAU<br>5.3.1<br>5.3.2                                                                                                                  | Top-Level Router-Switch         Link Unit         Controller         Exchange         JLT TOLERANCE - STAGE ONE         Stage One Enhancements to the Link Unit         Stage One Enhancements to the Controller         JLT TOLERANCE – STAGE TWO         Stage Two Enhancements to the Link Unit                                                                                                                                                                                                                                                                                                            | <i>97</i><br><i>97</i><br><i>101</i><br><i>106</i><br><i>107</i><br><i>107</i><br><i>110</i><br><i>111</i><br><i>111</i><br><i>112</i>        |

| 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.2 FAI<br>5.2.1<br>5.2.2<br>5.3 FAI<br>5.3.1<br>5.3.2<br>6 DESIG                                                                                                       | Top-Level Router-Switch.         Link Unit.         Controller         Exchange         JLT TOLERANCE - STAGE ONE.         Stage One Enhancements to the Link Unit.         Stage One Enhancements to the Controller         JLT TOLERANCE – STAGE TWO         Stage Two Enhancements to the Link Unit.         Stage Two Enhancements to the Controller                                                                                                                                                                                                                                                      | 97<br>97<br>101<br>106<br>107<br>107<br>110<br>111<br>111<br>112<br>112                                                                       |

| 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.2 FAI<br>5.2.1<br>5.2.2<br>5.3 FAI<br>5.3.1<br>5.3.2<br>6 DESIG                                                                                                       | Top-Level Router-Switch.         Link Unit.         Controller         Exchange         JLT TOLERANCE - STAGE ONE.         Stage One Enhancements to the Link Unit.         Stage One Enhancements to the Controller         JLT TOLERANCE – STAGE TWO         Stage Two Enhancements to the Link Unit.         Stage Two Enhancements to the Controller         Stage Two Enhancements to the Controller | 97<br>97<br>101<br>106<br>107<br>110<br>111<br>111<br>112<br><b>114</b>                                                                       |

| 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.2 FAU<br>5.2.1<br>5.2.2<br>5.3 FAU<br>5.3.1<br>5.3.2<br>6 DESIG<br>6.1 PRI                                                                                            | Top-Level Router-Switch.         Link Unit.         Controller         Exchange         JLT TOLERANCE - STAGE ONE.         Stage One Enhancements to the Link Unit.         Stage One Enhancements to the Controller         JLT TOLERANCE – STAGE TWO         Stage Two Enhancements to the Link Unit.         Stage Two Enhancements to the Controller         ELIMINARY SIMULATIONS                                                                     | 97<br>97<br>101<br>106<br>107<br>110<br>111<br>111<br>112<br><b>114</b><br>114                                                                |

| 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.2 FAU<br>5.2.1<br>5.2.2<br>5.3 FAU<br>5.3.1<br>5.3.2<br>6 DESIG<br>6.1 PRI<br>6.1.1<br>6.1.2                                                                          | Top-Level Router-Switch.         Link Unit.         Controller         Exchange         JLT TOLERANCE - STAGE ONE.         Stage One Enhancements to the Link Unit.         Stage One Enhancements to the Controller         JLT TOLERANCE – STAGE TWO         Stage Two Enhancements to the Link Unit.         Stage Two Enhancements to the Link Unit.         Stage Two Enhancements to the Controller         N SYNTHESIS & VERIFICATION         ELIMINARY SIMULATIONS         Credit-based and Permission-based Flow Control Comparison Analysis.                                                        | 97<br>97<br>101<br>106<br>107<br>110<br>111<br>111<br>112<br>114<br>114<br>114<br>114                                                         |

| 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.2 FAU<br>5.2.1<br>5.2.2<br>5.3 FAU<br>5.3.1<br>5.3.2<br>6 DESIG<br>6.1 PRI<br>6.1.1<br>6.1.2<br>6.2 BA<br>6.2.1                                                       | Top-Level Router-Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 97<br>97<br>101<br>106<br>107<br>110<br>111<br>111<br>112<br>114<br>114<br>114<br>114<br>119<br>119                                           |

| 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.2 FAU<br>5.2.1<br>5.2.2<br>5.3 FAU<br>5.3.1<br>5.3.2<br>6 DESIG<br>6.1 PRI<br>6.1.1<br>6.1.2<br>6.2 BA<br>6.2.1<br>6.2.1.                                             | Top-Level Router-Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 97<br>97<br>101<br>106<br>107<br>107<br>110<br>111<br>111<br>112<br>114<br>114<br>114<br>114<br>119<br>119                                    |

| 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.2 FAU<br>5.2.1<br>5.2.2<br>5.3 FAU<br>5.3.1<br>5.3.2<br>6 DESIG<br>6.1 PRI<br>6.1.1<br>6.1.2<br>6.2 BA<br>6.2.1<br>6.2.1.                                             | Top-Level Router-Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 97<br>97<br>101<br>106<br>107<br>107<br>110<br>111<br>111<br>112<br>114<br>114<br>114<br>114<br>114<br>119<br>119<br>120                      |

| 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.2 FAU<br>5.2.1<br>5.2.2<br>5.3 FAU<br>5.3.1<br>5.3.2<br>6 DESIG<br>6.1 PRI<br>6.1.1<br>6.1.2<br>6.2 BA<br>6.2.1<br>6.2.1<br>6.2.1<br>6.2.1<br>6.2.2                   | Top-Level Router-Switch         Link Unit         Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 97<br>97<br>101<br>106<br>107<br>110<br>111<br>111<br>112<br>114<br>114<br>114<br>114<br>114<br>119<br>119<br>120<br>128                      |

| 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.2 FAU<br>5.2.1<br>5.2.2<br>5.3 FAU<br>5.3.1<br>5.3.2<br>6 DESIG<br>6.1 PRI<br>6.1.1<br>6.1.2<br>6.2 BA<br>6.2.1<br>6.2.1<br>6.2.1<br>6.2.1<br>6.2.2<br>6.2.3          | Top-Level Router-Switch         Link Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 97<br>97<br>101<br>106<br>107<br>110<br>111<br>111<br>112<br>114<br>114<br>114<br>114<br>114<br>119<br>119<br>119<br>120<br>128<br>130        |

| 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.2 FAU<br>5.2.1<br>5.2.2<br>5.3 FAU<br>5.3.1<br>5.3.2<br>6 DESIG<br>6.1 PRI<br>6.1.1<br>6.1.2<br>6.2 BA<br>6.2.1<br>6.2.1<br>6.2.1<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.3 | Top-Level Router-Switch         Link Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 97<br>97<br>101<br>106<br>107<br>110<br>111<br>111<br>112<br>114<br>114<br>114<br>114<br>114<br>119<br>119<br>119<br>120<br>128<br>130<br>130 |

| 5.1.1 $5.1.2$ $5.1.3$ $5.1.4$ $5.2 FAU$ $5.2.1$ $5.2.2$ $5.3 FAU$ $5.3.1$ $5.3.2$ $6 DESIG$ $6.1 PRI$ $6.1.1$ $6.1.2$ $6.2 BA$ $6.2.1$ $6.2.1$ $6.2.1$ $6.2.1$ $6.2.3$ $6.2.3$ $6.2.3$                      | Top-Level Router-Switch         Link Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 97<br>97<br>101<br>106<br>107<br>110<br>111<br>111<br>112<br>114<br>114<br>114<br>114<br>119<br>119<br>119<br>120<br>128<br>130<br>130<br>133 |

IV

and a second sec

4. ~ 50 a 4.

Sec. 84.

the of a la way way

all's all as here.

and in Links -

1

S. w. .

| 6.3.1     | Stage Two Simulation                            | 135 |

|-----------|-------------------------------------------------|-----|

| 7 DISCUS  | SION, CONCLUSIONS AND FURTHER WORK              | 138 |

|           | USSION                                          |     |

|           | Fault tolerant features                         |     |

|           | Link Fault Detection and Recovery               |     |

|           | Deadlock handling procedures                    |     |

|           | Basic Routing Features                          |     |

|           | Flow Control Mechanisms                         |     |

| 7.1.2.2   |                                                 |     |

| 7.1.2.3   | Connection servicing                            |     |

| 7.1.2.4   | Network Configuration                           | 149 |

| 7.2 CON   | CLUSIONS                                        | 149 |

| 7.3 FURT  | THER WORK                                       | 152 |

| 7.3.1     | System Level Work                               | 153 |

| 7.3.2     | Further Routing Techniques                      | 153 |

| PUBLICATI | ONS                                             | 157 |

| REFERENC  | ES                                              | 158 |

| APPENDIX  | A : PRELIMINARY FLOW CONTROL COMPARISON RESULTS | A-1 |

| APPENDIX  | B : BASIC STOP/GO ANALYSIS DETAILS              | B-1 |

| APPENDIX  | C : NTR-FTM08 PERFORMANCE RESULTS               | C-1 |

| APPENDIX  | D : ANALYSIS UTILITIES                          | D-1 |

| APPENDIX  | E : HARDWARE TEST DESCRIPTIONS                  | E-1 |

| APPENDIX  | F : DEADLOCK DETECTION MECHANISM DETAILS        | F-1 |

### LIST OF ACRONYMS

| ASIC      | Application Specific Integrated Circuit                               |

|-----------|-----------------------------------------------------------------------|

| CAN       | Controller Area Network (serial bus-based communication system)       |

| CRC       | Cyclic Redundancy Check                                               |

| CSP       | Communicating Sequential Processes                                    |

| DSP       | digital signal processing                                             |

| FIFO      | First In First Out                                                    |

| HDL       | Hardware Description Language                                         |

| IEEE      | Institute of Electrical and Electronic Engineers                      |

| IP        | Intellectual Property                                                 |

| ISO       | International Standards Organisation                                  |

| LAN       | Local Area Network                                                    |

| Mb/s      | Megabits per second                                                   |

| MB/s      | Megabytes per second                                                  |

| MIMD      | Multiple Instruction, Multiple Data                                   |

| NRZ-M     | Non-Return to Zero Mark (also known as NRZ-I – Invert)                |

| NTR08     | A dynamic packet routing device, which resulted from earlier research |

| NTR-FTM08 | The dynamic packet routing device produced by this research           |

| NTR-M04   | A dynamic packet routing device, which resulted from earlier research |

| OSI       | Open Systems Interconnect                                             |

| PLD       | Programmable Logic Device                                             |

| SAN       | Small Area Network                                                    |

| SIMD      | Single Instruction Multiple Data                                      |

| UART      | Universal Asynchronous Receiver Transmitter                           |

| USB       | Universal Serial Bus                                                  |

| VHDL      | Very high speed integrated circuit Hardware Description Language      |

| VLIW      | Very Long Instruction Word                                            |

| VLSI      | Very Large Scale Integration                                          |

| WAN       | Wide Area Network                                                     |

| X-OFF     | Transmit off (also referred to as STOP)                               |

| X-ON      | Transmit on (also referred to as GO)                                  |

| XOR       | exclusive OR                                                          |

|           |                                                                       |

## LIST OF FIGURES

| FIGURE 2-1 : AN EXAMPLE OF FIVE TIMES OVER-SAMPLING                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

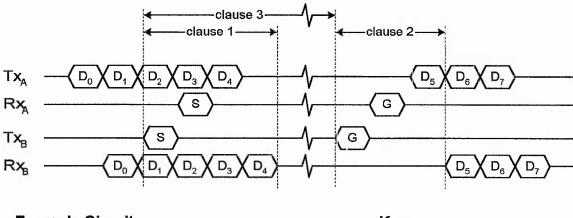

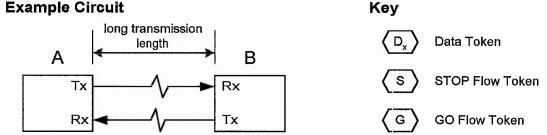

| FIGURE 2-2 : DEPICTION OF THE STOP/GO FLOW CONTROL MECHANISM WITH THE IMPORTANT FEATURES<br>INDICATED THAT MUST BE REGULATED FOR CORRECT OPERATION                                                                   |

| FIGURE 2-3 : REPRESENTATION OF THE BUFFERING REQUIRED FOR THE STOP/GO FLOW CONTROL MECHANISM                                                                                                                         |

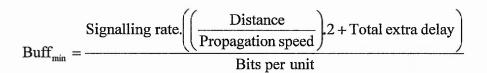

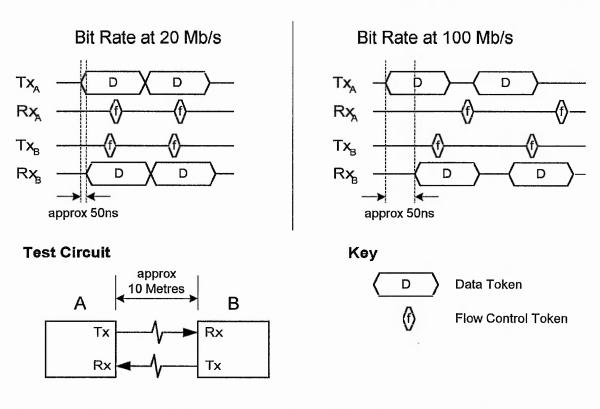

| FIGURE 2-4 : DEPICTION OF THE OPERATION OF A CREDIT BASED FLOW CONTROL MECHANISM OVER 10 METRES<br>AT 20 MB/s (left) and operation over 10 metres at 100 MB/s (right) showing the appropriate<br>transmission delays |

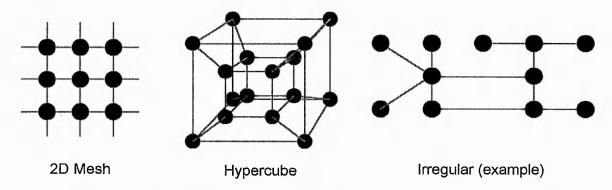

| FIGURE 2-5 : DEPICTION OF THE INTERCONNECTION STRUCTURE OF THE 2D MESH AND HYPERCUBE<br>TOPOLOGIES, AND AN EXAMPLE IRREGULAR NETWORK                                                                                 |

| FIGURE 2-6 : GENERIC PACKET FORMAT USED AS A BASIS FOR THE MAJORITY OF PROTOCOLS                                                                                                                                     |

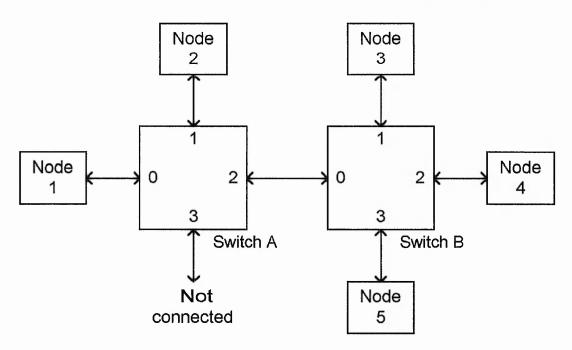

| FIGURE 2-7 : DEPICTION OF A THEORETICAL NETWORK SHOWING FIVE COMMUNICATING NODES CONNECTED<br>VIA TWO, FOUR-PORT SWITCHES                                                                                            |

| FIGURE 2-8 : DEPICTION OF DEADLOCK IN A FOUR NODE SYSTEM                                                                                                                                                             |

| FIGURE 3-1 : A DIAGRAM OF THE SPLIT LINK OPERATION OF THE NTR-M04                                                                                                                                                    |

| FIGURE 3-2 : OS LINK PROTOCOL BASE TOKENS                                                                                                                                                                            |

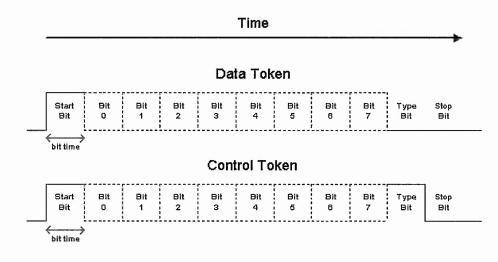

| FIGURE 3-3 : FORMAT OF THE DATA AND CONTROL TOKENS OF THE DS PROTOCOL                                                                                                                                                |

| FIGURE 3-4 : TOKEN FORMAT USED IN THE NTR-M04 PROTOCOL                                                                                                                                                               |

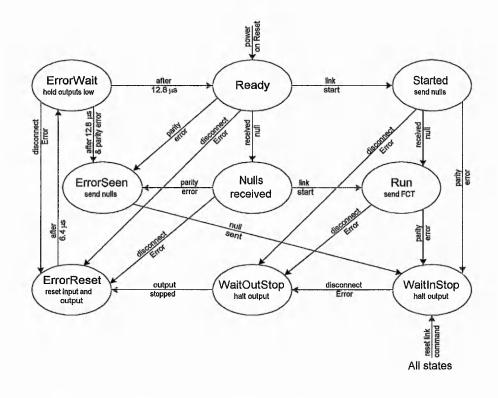

| FIGURE 3-5 : LINK STATE MACHINE FOR THE IEEE STD. 1355-199560                                                                                                                                                        |

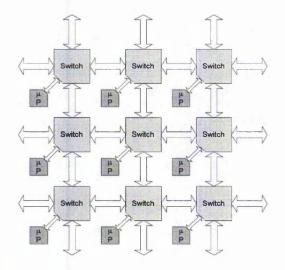

| FIGURE 3-6 : PREVALENT MESH TOPOLOGY USED WITH 4+1 PORT ROUTER-SWITCHES FOR HIGH-PERFORMANCE<br>PARALLEL PROCESSING                                                                                                  |

| FIGURE 3-7 : DEPICTION OF AN ALLOCATION DEADLOCK SCENARIO                                                                                                                                                            |

| FIGURE 3-8 : PACKET STRUCTURE USED IN THE HYBRID PROTOCOL OF THE NTR08                                                                                                                                               |

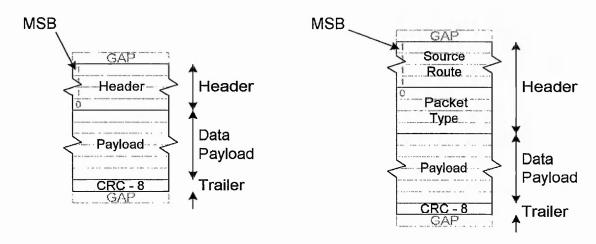

| FIGURE 3-9 : PACKET FORMAT FOR THE FIRST GENERATION (LEFT) AND SECOND GENERATION (RIGHT) OF<br>MYRINET                                                                                                               |

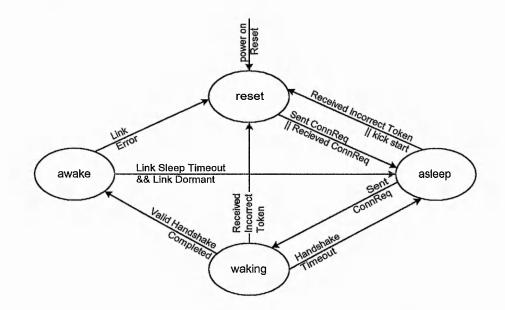

| FIGURE 4-1 : FINITE STATE MACHINE FOR THE NTR-FTM08 LINK STATUS                                                                                                                                                      |

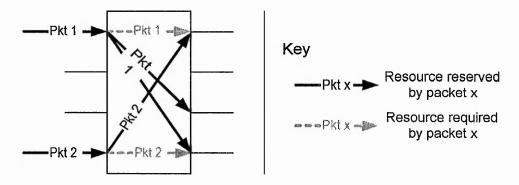

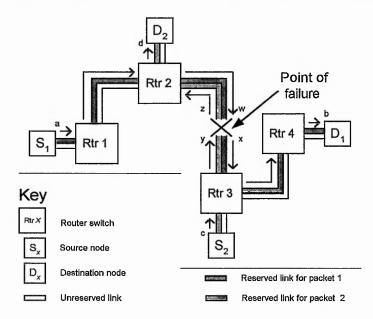

| FIGURE 4-2 : THEORETICAL NETWORK WITH A SINGLE POINT OF FAILURE, SHOWING ALLOCATED RESOURCES 86                                                                                                                      |

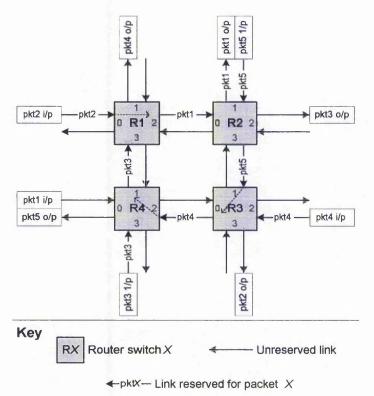

| FIGURE 4-3 : A DEPICTION OF AN EXAMPLE NETWORK PRIOR TO THE FORMATION OF A DEADLOCK CYCLE91                                                                                                                          |

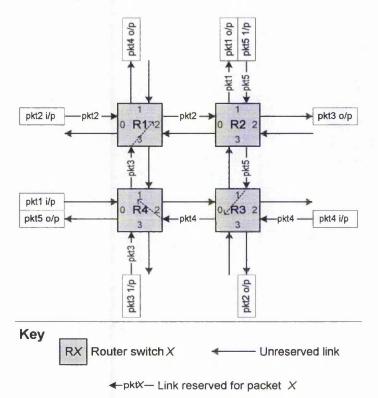

| FIGURE 4-4 : INTRODUCTION OF A FOURTH PACKET INTO AND EXAMPLE NETWORK PRIOR TO THE FORMATION<br>OF A DEADLOCK CYCLE                                                                                                  |

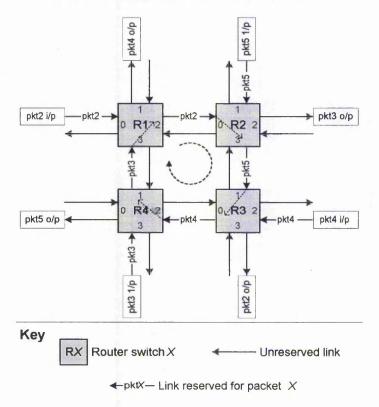

| FIGURE 4-5 : THE ENTRY OF THE THIRD PACKET IN THE FORMATION OF A DEADLOCK CYCLE                                                                                                                                      |

| FIGURE 4-6 : DEPICTION OF THE FINAL STAGES OF THE FORMATION OF A DEADLOCK CYCLE                                                                                                                                      |

| FIGURE 4-7 : THE COMPLETE DEADLOCK CYCLE95                                                                                                                                                                           |

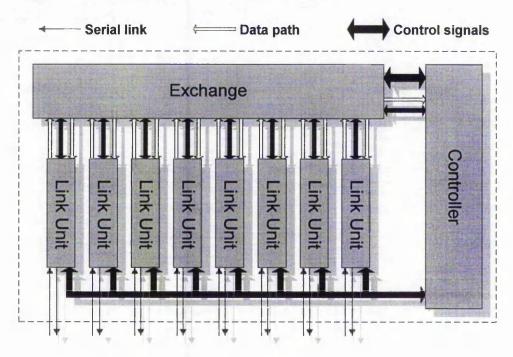

| FIGURE 5-1 : BLOCK DIAGRAM OF THE TOP LEVEL COMPONENTS OF THE NTR-FTM0897                                                                                                                                            |

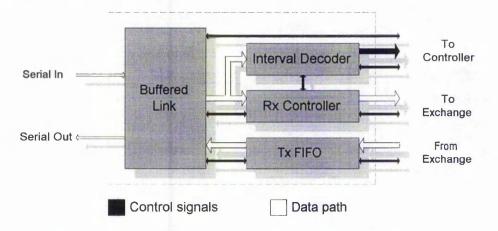

| FIGURE 5-2 : BLOCK DIAGRAM OF THE LINK UNIT OF THE NTR-FTM0898                                                                                                                                                       |

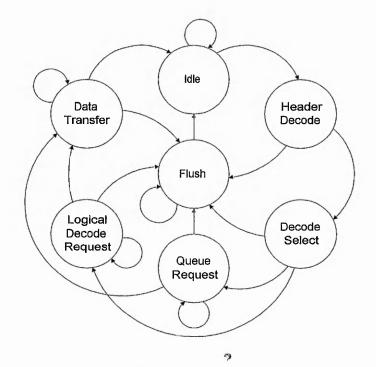

| FIGURE 5-3 : RECEIVER CONTROLLER FINITE STATE MACHINE                                                                                                                                       | .99 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

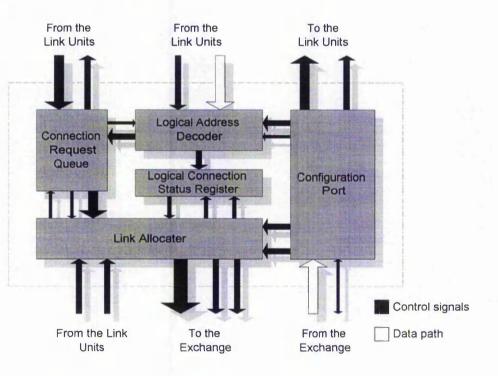

| FIGURE 5-4 : BLOCK DIAGRAM OF THE CONTROLLER OF THE NTR-FTM08 1                                                                                                                             | 101 |

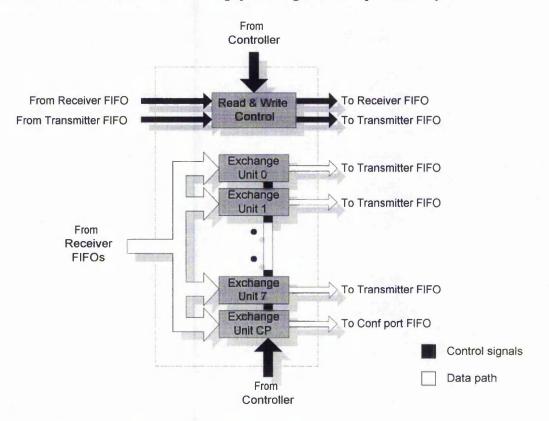

| FIGURE 5-5 : BLOCK DIAGRAM OF THE EXCHANGE OF THE NTR-FTM08 I                                                                                                                               | 106 |

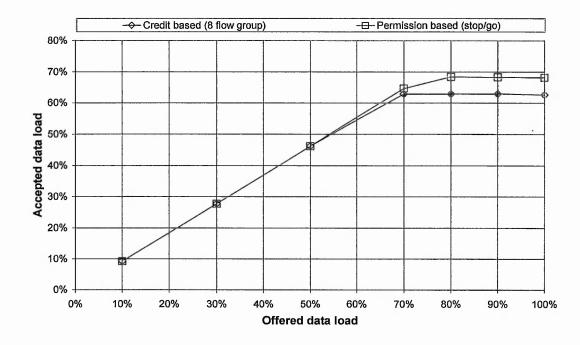

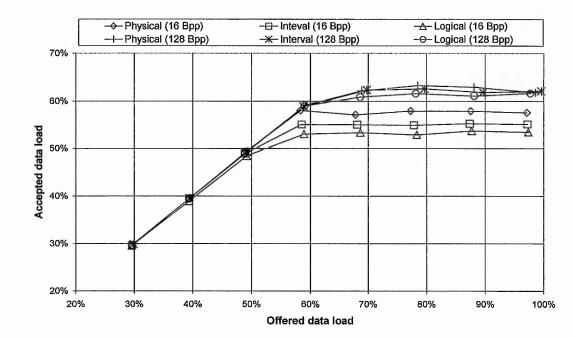

| FIGURE 6-1 : OFFERED LOAD VERSES ACCEPTED LOAD FOR A BEHAVIOURAL MODEL OF A FOUR PORT ROUTEF<br>SWITCH FOR PERMISSION AND CREDIT BASED FLOW CONTROL                                         | -   |

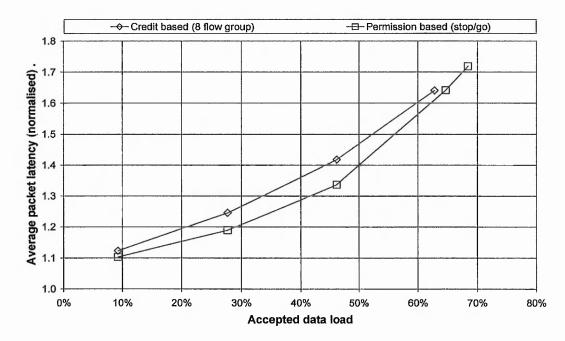

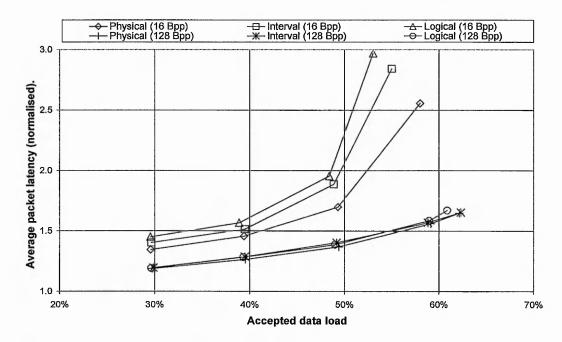

| FIGURE 6-2 : ACCEPTED DATA LOAD VERSES AVERAGE PACKET LATENCY FOR A BEHAVIOURAL MODEL OF A FOUR PORT ROUTER-SWITCH FOR PERMISSION AND CREDIT BASED FLOW CONTROL                             | 116 |

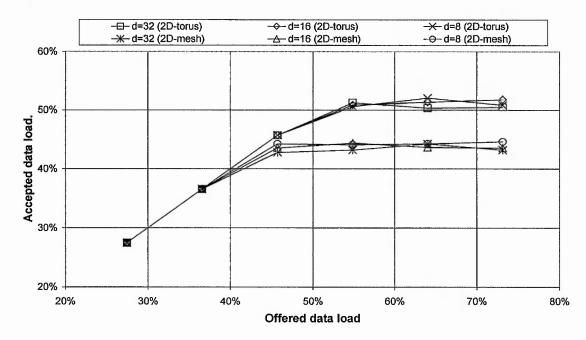

| FIGURE 6-3 : OFFERED DATA LOAD VERSES ACCEPTED DATA LOAD OVER A RANGE OF WORKLOADS FOR A<br>TORUS AND MESH NETWORK WITH VARIATION ON THE FLOW CONTROL THRESHOLD VALUE DIFFERENTIA<br>       |     |

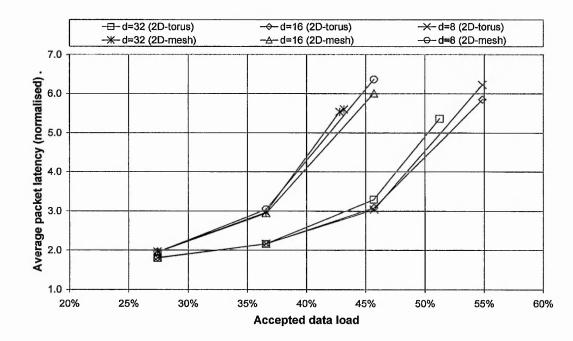

| FIGURE 6-4 : ACCEPTED DATA LOAD VERSES AVERAGE PACKET LATENCY OVER A RANGE OF WORKLOADS FO<br>A TORUS AND MESH NETWORK WITH VARIATION ON THE FLOW CONTROL THRESHOLD VALUE<br>DIFFERENTIAL   |     |

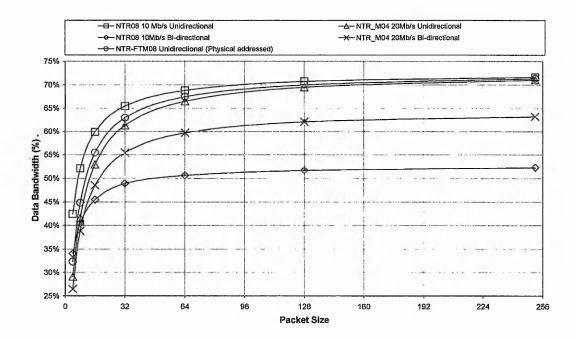

| FIGURE 6-5 : SIMULATION RESULTS FOR RAW BANDWIDTH COMPARISON WITH THE EARLIER DEVICES OF AN UNLOADED NETWORK                                                                                | 21  |

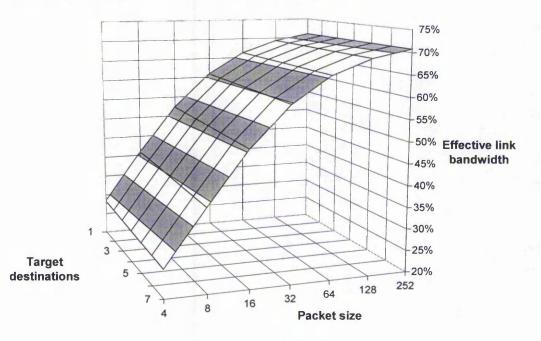

| FIGURE 6-6 : UNLOADED NETWORK, RAW BANDWIDTH COMPARISON OF EFFECTIVE LINK BANDWIDTH FOR<br>MULTICAST CONNECTIONS                                                                            | 122 |

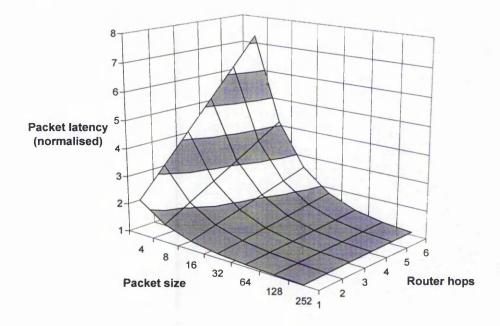

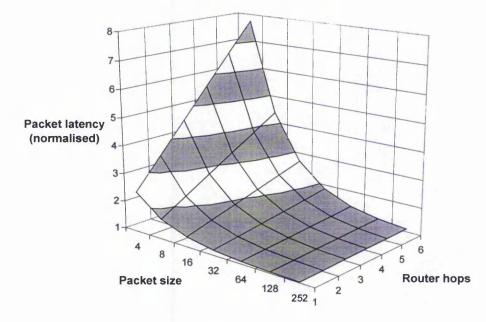

| FIGURE 6-7 : PACKET LATENCY VERSES ROUTER-SWITCH HOPS AND PACKET SIZE FOR PHYSICAL ADDRESSED<br>PACKETS                                                                                     |     |

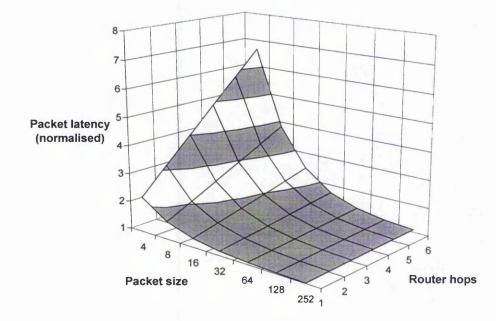

| FIGURE 6-8 : PACKET LATENCY VERSES ROUTER-SWITCH HOPS AND PACKET SIZE FOR INTERVAL ADDRESSED<br>PACKETS                                                                                     |     |

| FIGURE 6-9 : PACKET LATENCY VERSES ROUTER-SWITCH HOPS AND PACKET SIZE FOR LOGICAL ADDRESSED<br>PACKETS                                                                                      | 124 |

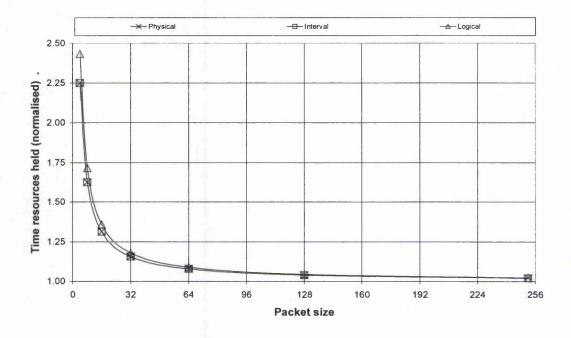

| FIGURE 6-10 : TIME RESOURCES ARE HELD FOR A PACKET RELATIVE TO THE PACKET SIZE FOR A SINGLE<br>ROUTING HEADER FOR INTERVAL, LOGICAL AND PHYSICAL ADDRESSED PACKET IN AN UNLOADED<br>NETWORK | 125 |

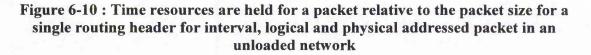

| FIGURE 6-11 : TIME RESOURCES THAT ARE HELD FOR A PHYSICALLY ADDRESSED PACKET RELATIVE TO THE PACKET SIZE FOR CONNECTIONS OVER 1 TO 6 ROUTER-SWITCHES IN AN UNLOADED NETWORK                 | 125 |

| FIGURE 6-12 : OFFERED DATA LOAD VERSES ACCEPTED DATA LOAD OVER A RANGE OF WORKLOADS FOR A SINGLE ROUTER-SWITCH FOR 16 AND 128 BYTE PACKETS                                                  | 127 |

| FIGURE 6-13 : ACCEPTED DATA LOAD VERSES AVERAGE PACKET TIME OVER A RANGE OF WORKLOADS FOR A SINGLE ROUTER-SWITCH FOR 16 AND 128 BYTE PACKETS                                                | -   |

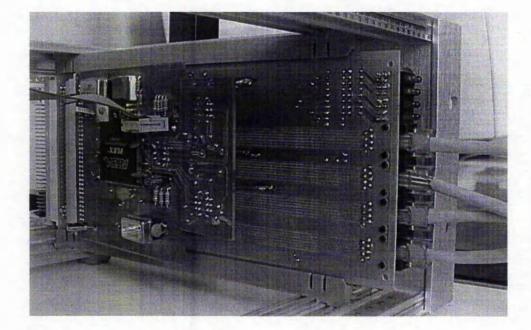

| FIGURE 6-14 : A PHOTOGRAPH OF THE NTR-FTM08 PROTOTYPE DEVICE AND DRIVER BOARD                                                                                                               | 29  |

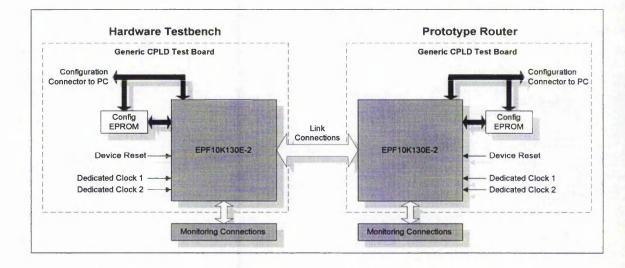

| FIGURE 6-15 : BLOCK DIAGRAM OF THE HARDWARE USED FOR VERIFICATION TESTS                                                                                                                     | 131 |

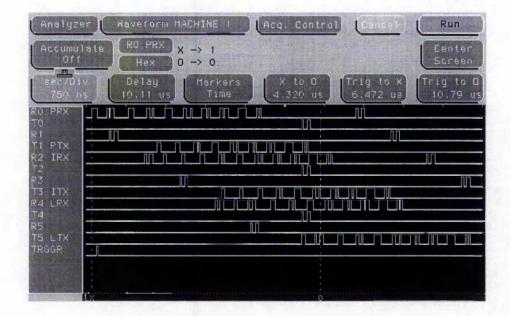

| FIGURE 6-16 : A CAPTURED TRACE FROM THE UNLOADED ROUTER-SWITCH TESTS FOR ALL THREE ADDRESSIN<br>MODES FOR UNIDIRECTIONAL DATA FLOW                                                          |     |

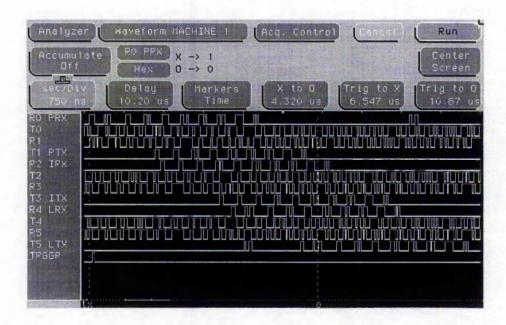

| FIGURE 6-17 : A CAPTURED TRACE FROM THE UNLOADED ROUTER-SWITCH TESTS FOR ALL THREE ADDRESSIN<br>MODES FOR BI-DIRECTIONAL DATA FLOW                                                          |     |

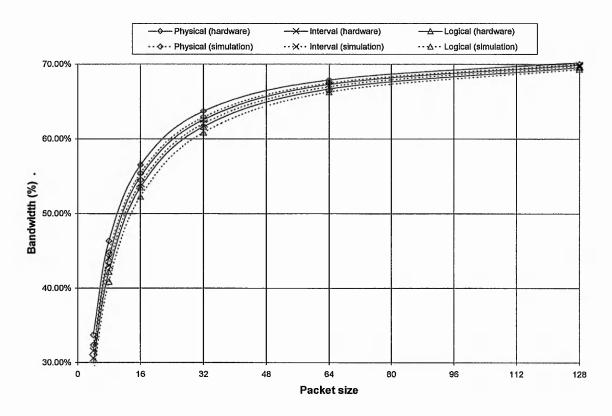

| FIGURE 6-18 : HARDWARE RESULTS FOR RAW BANDWIDTH COMPARISON WITH THE EARLIER DEVICES OF AN UNLOADED NETWORK                                                                                 | 135 |

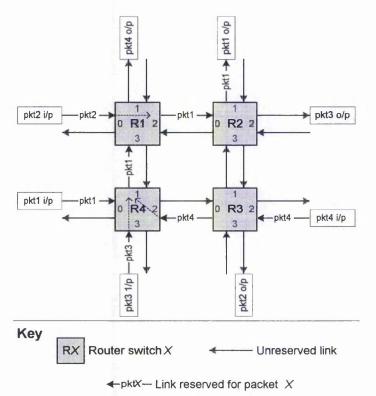

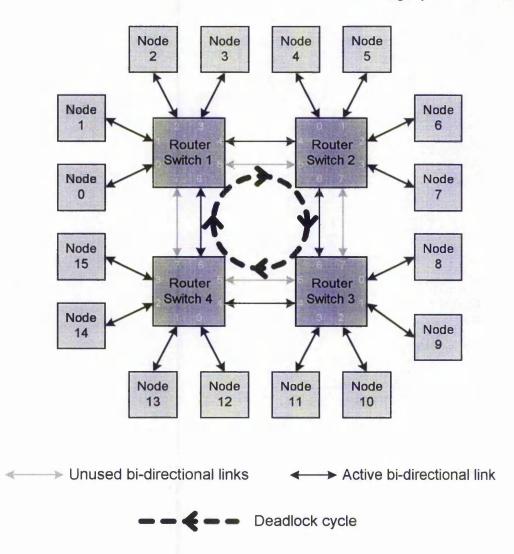

| FIGURE 6-19 : NETWORK STRUCTURE USED FOR DEADLOCK TESTING                                                                                                                                   | 136 |

\$

### LIST OF TABLES

| TABLE 2-1 : CONFIGURATION DETAILS FOR SWITCHES A (LEFT) AND B (RIGHT) IN THE NETWORK AS DEPICTED         IN FIGURE 2-7                |

|---------------------------------------------------------------------------------------------------------------------------------------|

| TABLE 2-2 : INTERVAL CONFIGURATION FOR SWITCHES A (LEFT) AND B (RIGHT) IN THE NETWORK AS         DEPICTED IN FIGURE 2-7               |

| TABLE 2-3 : VALID ROUTING HEADERS FOR RELATIVE ADDRESSING FOR A FOUR-PORT SWITCH                                                      |

| TABLE 3-1 : LIST OF ALL TYPE OF TOKEN USED IN THE DS LINK PROTOCOL       52                                                           |

| TABLE 3-2 : LIST OF ALL DEFINED TYPES OF TOKEN USED IN THE NETWORK LAYER OF THE NTR-M04         PROTOCOL                              |

| TABLE 3-3 : LIST OF ALL DEFINED TYPES OF TOKEN USED IN THE FIRST GENERATION MYRINET PROTOCOL 54                                       |

| TABLE 3-4 : LIST OF ALL DEFINED TYPES OF TOKEN USED IN THE SECOND GENERATION MYRINET LAN         PROTOCOL                             |

| TABLE 3-5 : FRAME FORMAT USE FOR THE RELIABLE ROUTER AS ONE FLOW CONTROL UNIT                                                         |

| TABLE 4-1 : DEFINITION OF THE BASIC TOKENS FOR THE NTR-FT08                                                                           |

| TABLE 4-2 : HEADER FORMAT FOR ADDRESSING MODES                                                                                        |

| TABLE 4-3 : DEFINITION OF THE EXTRA CONTROL TOKENS FOR STAGE ONE OF THE FAULT TOLERANCE         MECHANISM FOR THE NTR-FT08         82 |

| TABLE 4-4 : DEFINITION OF THE EXTRA CONTROL TOKENS FOR STAGE TWO OF THE FAULT TOLERANCE         MECHANISM FOR THE NTR-FTM08           |

| TABLE 5-1 : ATOMIC INSTRUCTIONS FOR THE CONFIGURATION PORT OF THE NTR-FTM08                                                           |

| TABLE 5-2 : EXAMPLE PACKET FOR CONFIGURATION OF THE NTR-FTM08                                                                         |

| TABLE 5-3 : ADDITIONAL ATOMIC INSTRUCTION FOR THE CONFIGURATION PORT OF THE NTR-FTM08 111                                             |

| TABLE 6-1 : SYNTHESIS RESULTS FOR THE NTR-FTM08 ROUTER-SWITCH                                                                         |

#### 1 Introduction

The research detailed within this thesis is the investigation and development of a communication network for use in a distributed memory, message-passing architecture. The architecture under consideration is constructed using one or more multiport, dynamic, packet-routing switches, which have evolved from earlier communication systems research [1, 2]. The network is targeted towards small to medium scale embedded parallel or distributed processing systems. The primary aim of the work was to improve the flexibility and reliability of the network compared to previous implementations from the earlier research.

#### 1.1 Parallel Concepts

Multiprocessor systems have evolved a great deal since their inception. The impetus of their development was initially, and continues to be in part, the desire for increased performance over the limits set by the technology of the time. In the early years of computing, the cost effectiveness of such systems meant that only large organisations could afford the associated development costs. Meanwhile, the relative ease of development of single processor systems, in comparison to that of parallel systems, reduced costs and allowed a much shorter time to market, which made them much more accessible to a wider market. The shorter design cycle time and lower costs have resulted in a continued bias of single processor systems in the mainstream computing market, compared to the development of multiprocessor systems. This bias of 'single processor system' parts has, in recent years, encouraged research using these low-cost commercial devices in parallel systems [3, 4, 5, 6]. While these solutions will never produce results comparable to custom parallel processor systems, their utilisation provided great improvements over single processor systems. Using microprocessors that were designed for the single processor market has ensured lower development costs while keeping pace with the state of the art technology especially for small scale parallel systems.

Despite many parallel systems adopting the use of microprocessors designed for single processor systems, constant pressure on the manufactures of microprocessors to supply devices with the greatest performance has seen the adoption of parallel processing techniques in the processing core. Pipeline techniques were integrated first into mainstream processors in the mid to late 1980's. Examples of these were the INTEL 386/486 processors [7]. This was followed by super-scalar architectures that allowed

#### 1 Introduction